# LatticeECP3 Family Handbook

HB1009 Version 05.2, July 2013

# LatticeECP3 Family Handbook Table of Contents

May 2013

| Section I. LatticeECP3 Family Data Sheet       |     |

|------------------------------------------------|-----|

| Introduction                                   |     |

| Features                                       |     |

| Introduction                                   |     |

| Architecture                                   |     |

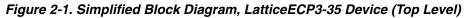

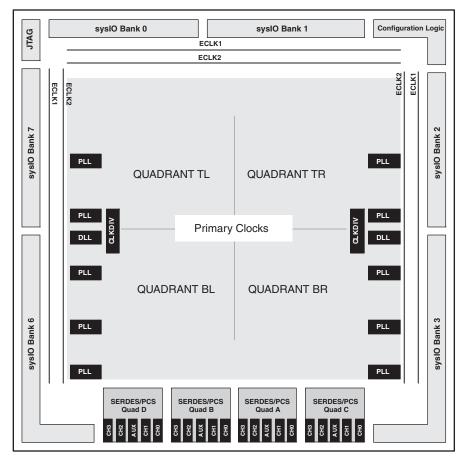

| Architecture Overview                          | 2-1 |

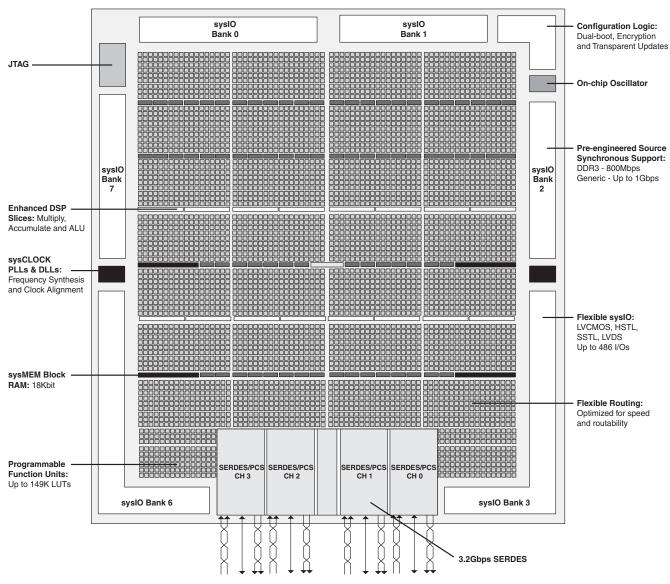

| PFU Blocks                                     |     |

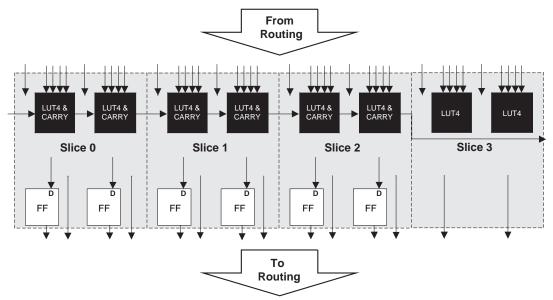

| Slice                                          |     |

| Modes of Operation                             | 2-5 |

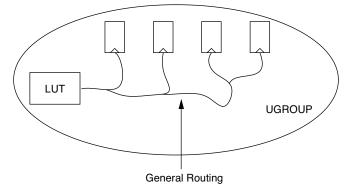

| Routing                                        |     |

| sysCLOCK PLLs and DLLs                         |     |

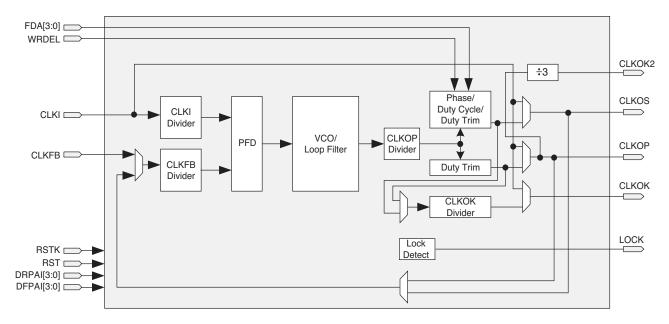

| General Purpose PLL                            |     |

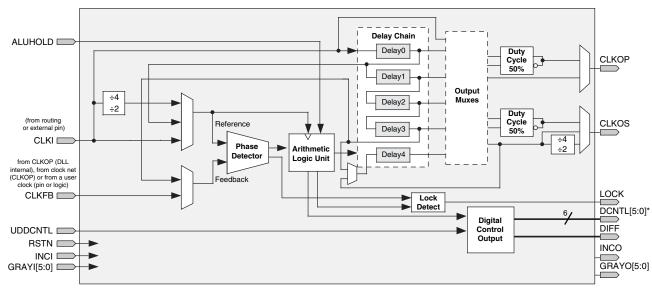

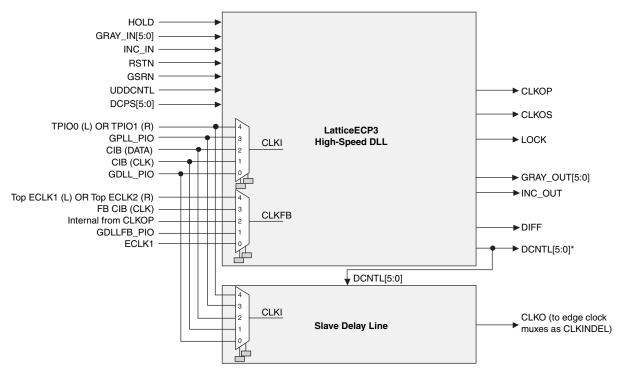

| Delay Locked Loops (DLL)                       |     |

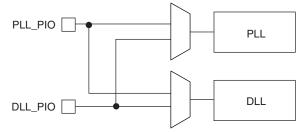

| PLL/DLL Cascading                              |     |

| PLL/DLL PIO Input Pin Connections              |     |

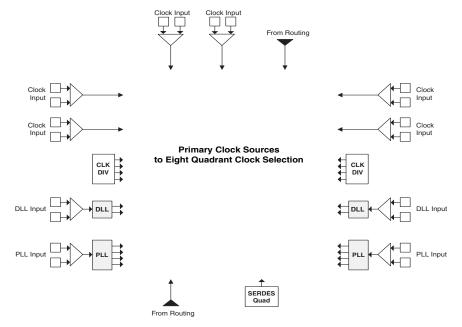

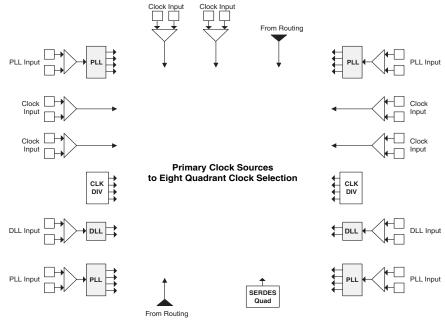

| Clock Dividers                                 |     |

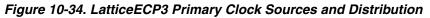

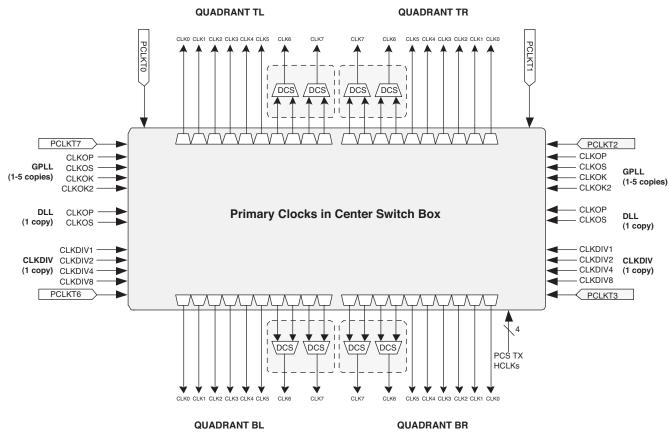

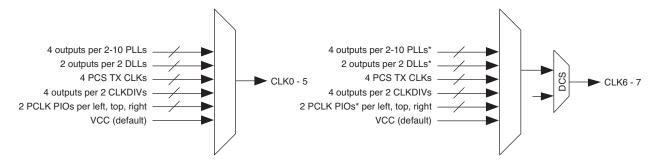

| Clock Distribution Network                     |     |

| Primary Clock Sources                          |     |

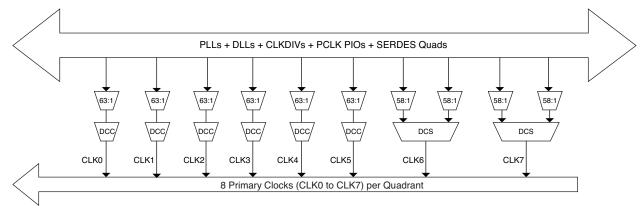

| Primary Clock Routing                          |     |

| Dynamic Clock Control (DCC)                    |     |

| Dynamic Clock Select (DCS)                     |     |

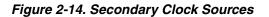

| Secondary Clock/Control Sources                |     |

| Secondary Clock/Control Routing                |     |

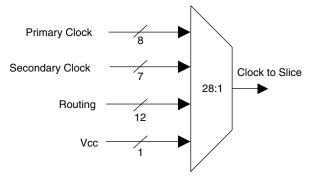

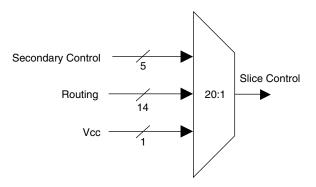

| Slice Clock Selection                          |     |

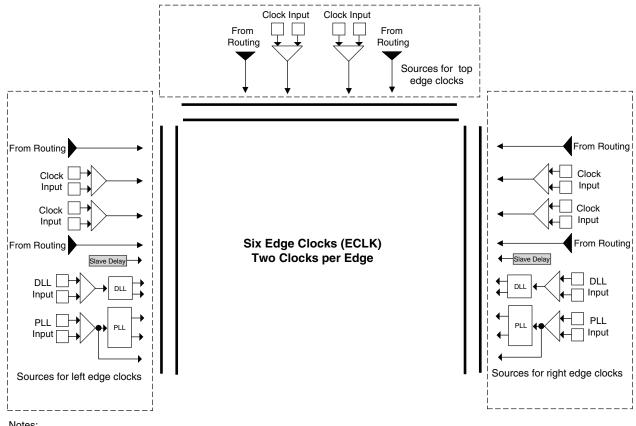

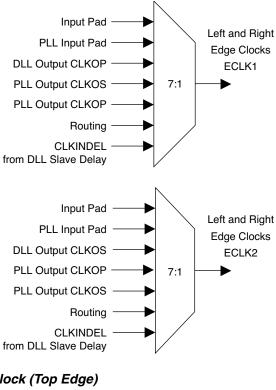

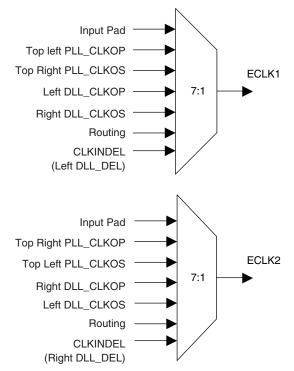

| Edge Clock Sources                             |     |

| Edge Clock Routing                             |     |

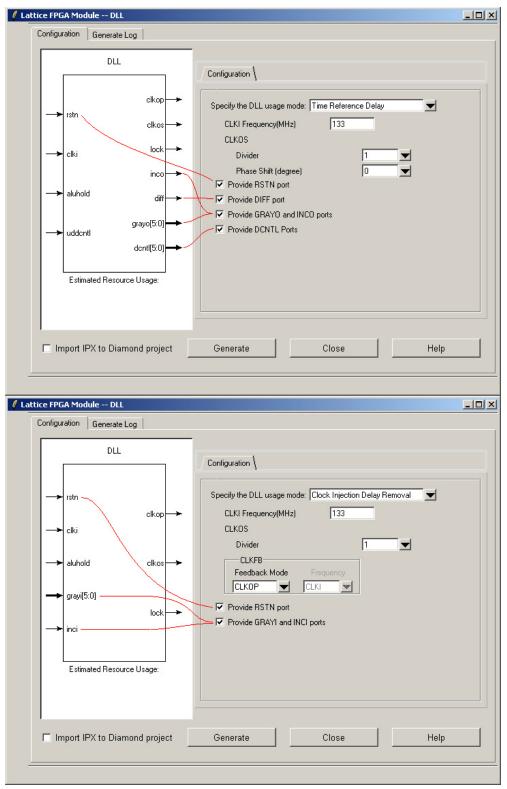

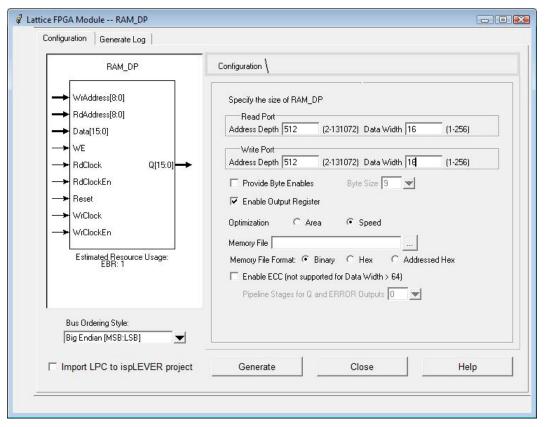

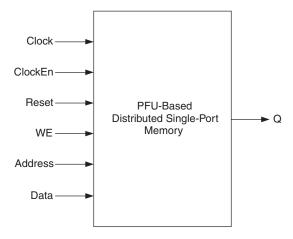

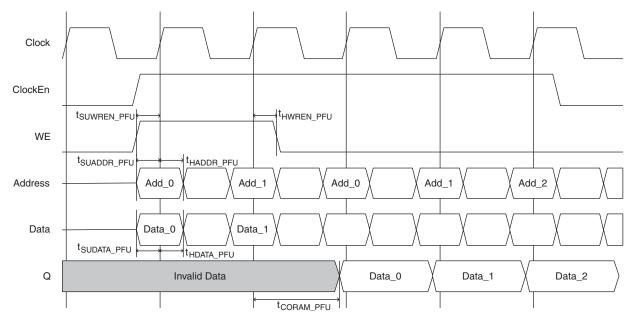

| sysMEM Memory                                  |     |

| sysMEM Memory Block                            |     |

| Bus Size Matching                              |     |

| RAM Initialization and ROM Operation           |     |

| Memory Cascading                               |     |

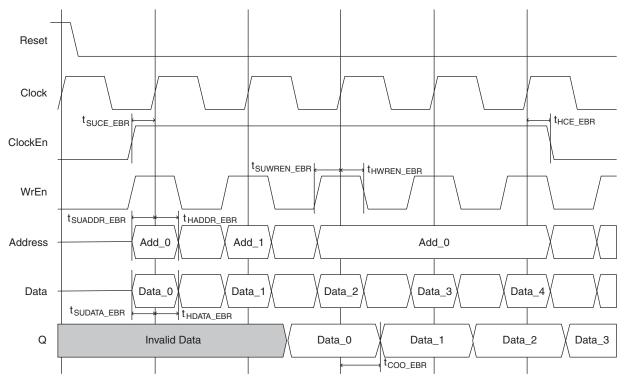

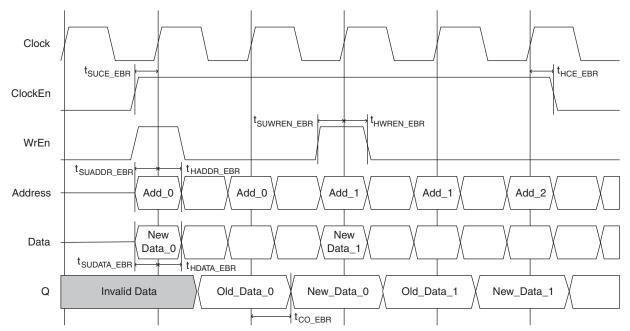

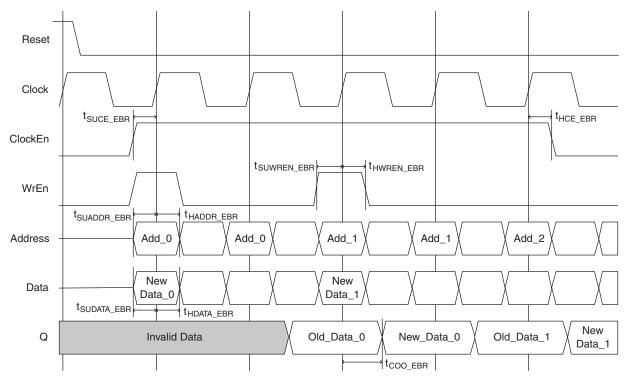

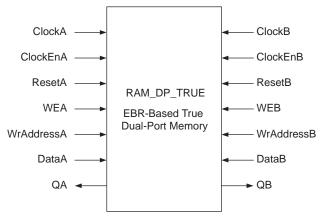

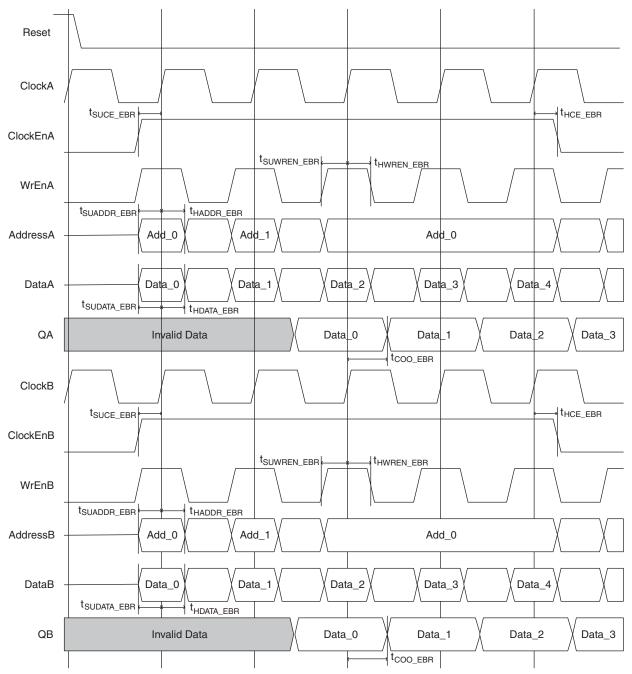

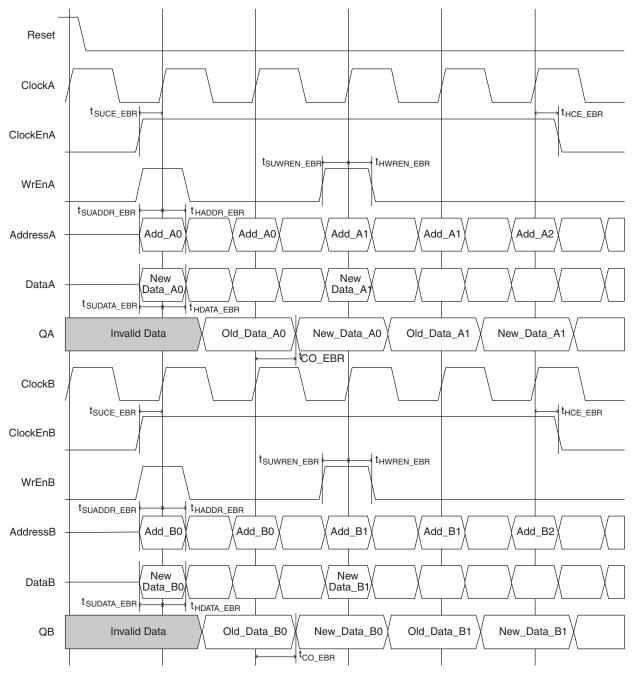

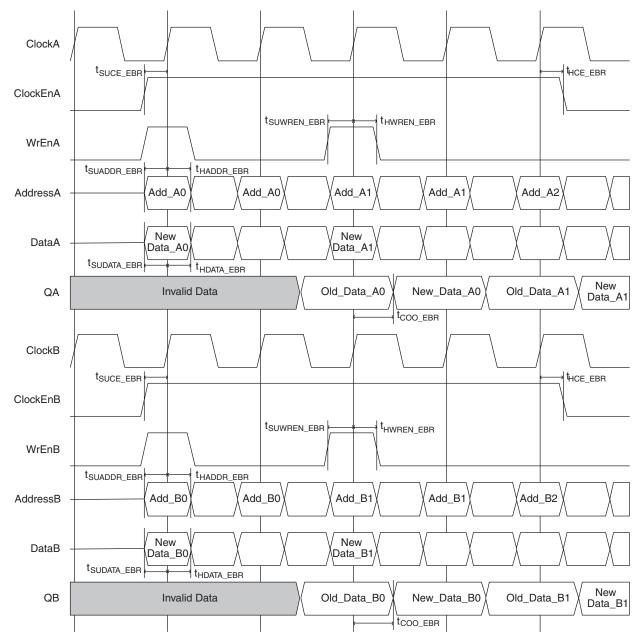

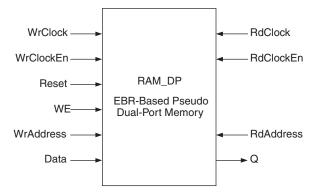

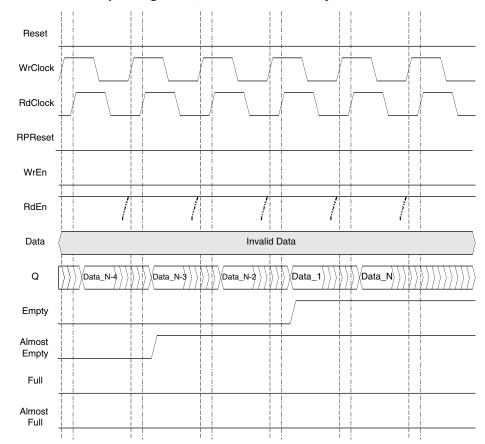

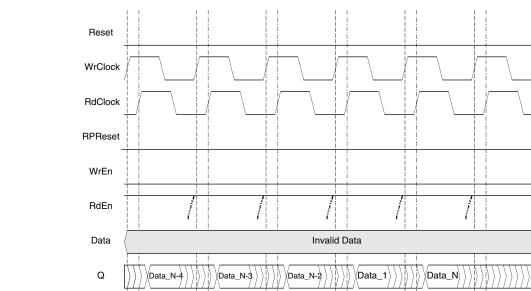

| Single, Dual and Pseudo-Dual Port Modes        |     |

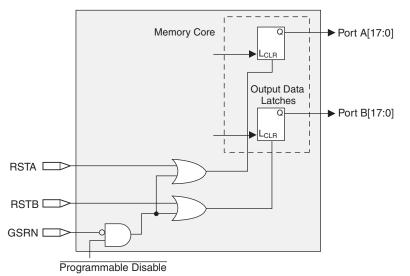

| Memory Core Reset                              |     |

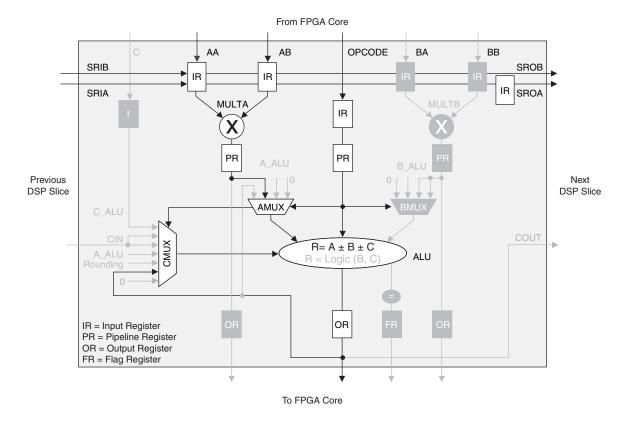

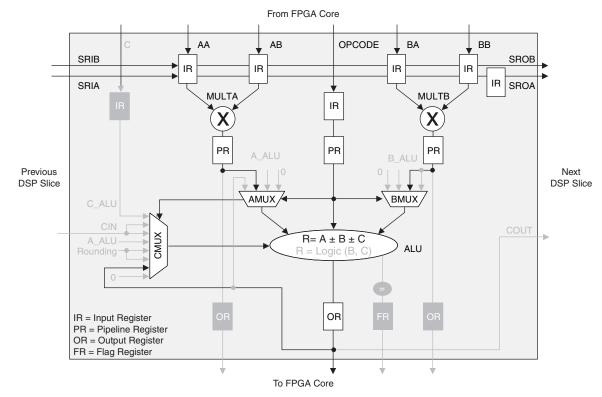

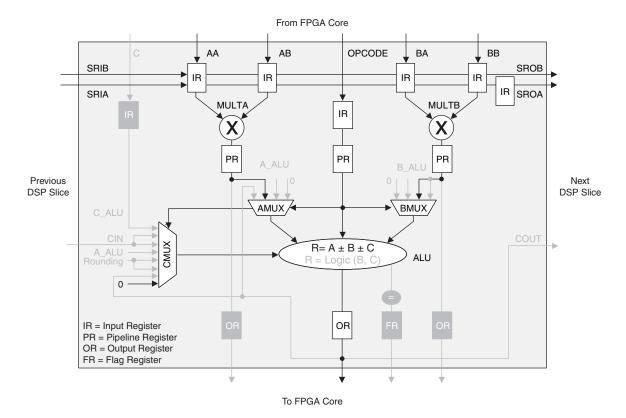

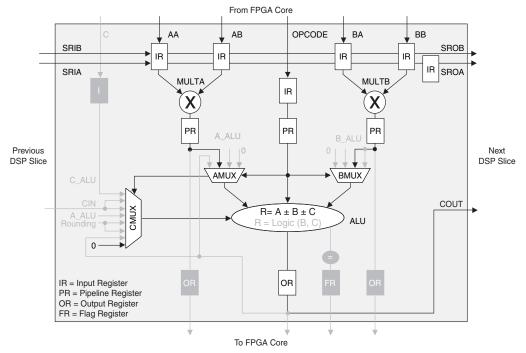

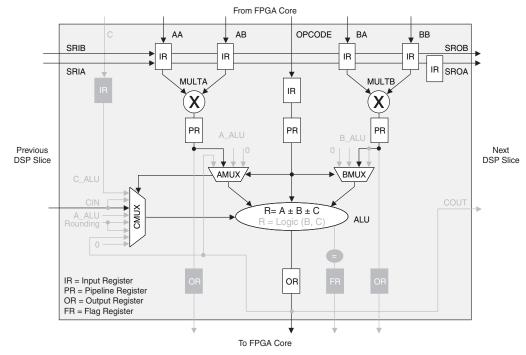

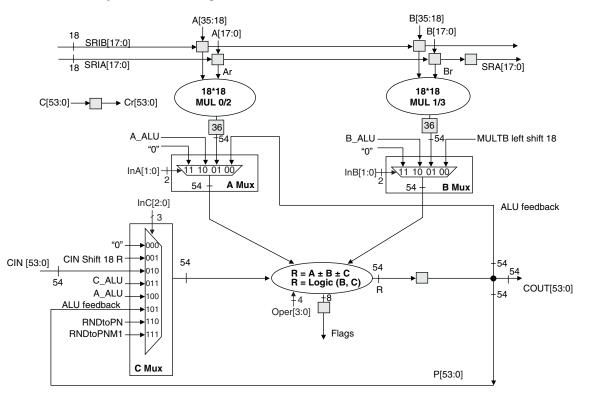

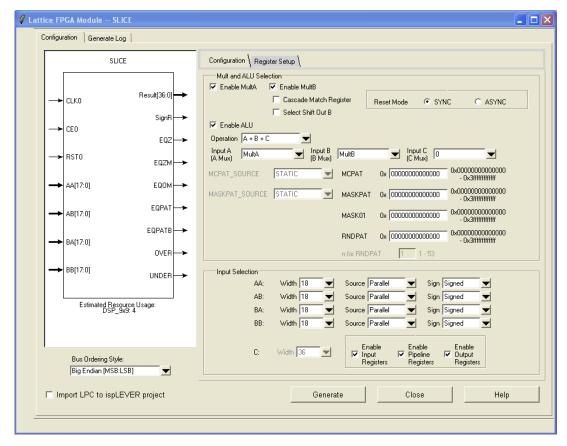

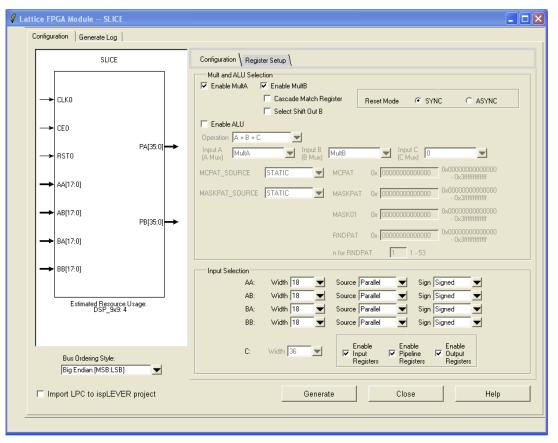

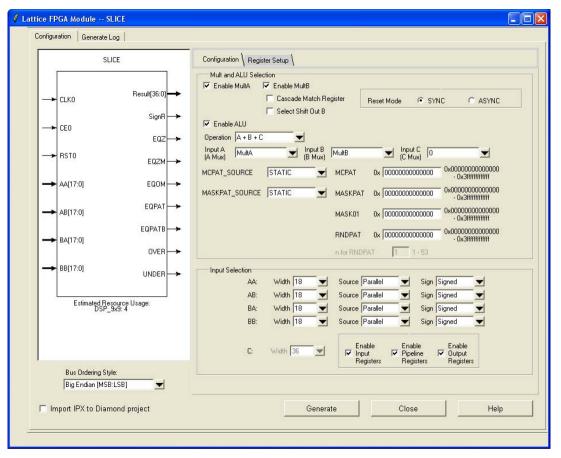

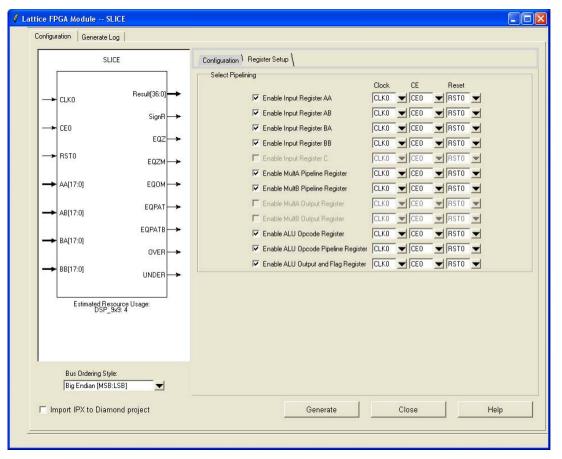

| sysDSP™ Slice                                  |     |

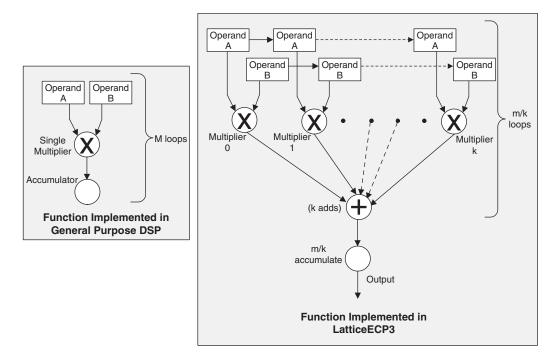

| sysDSP Slice Approach Compared to General DSP  |     |

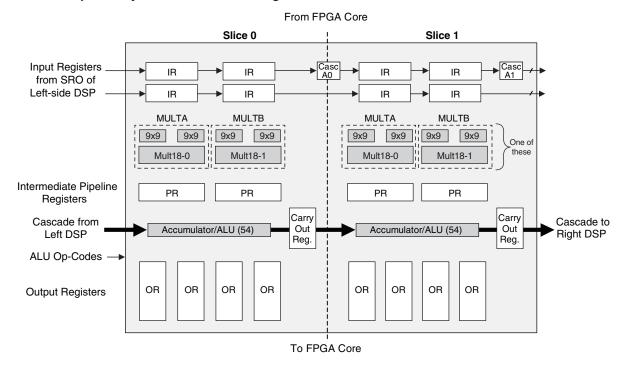

| LatticeECP3 sysDSP Slice Architecture Features |     |

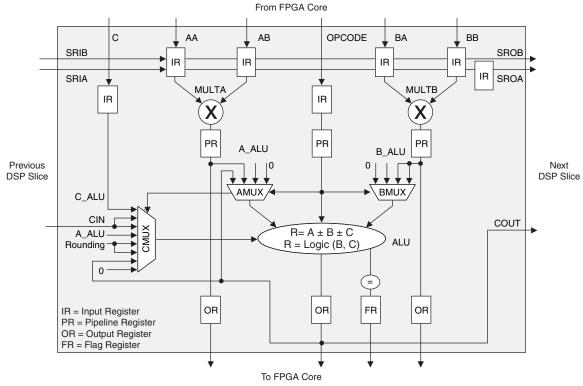

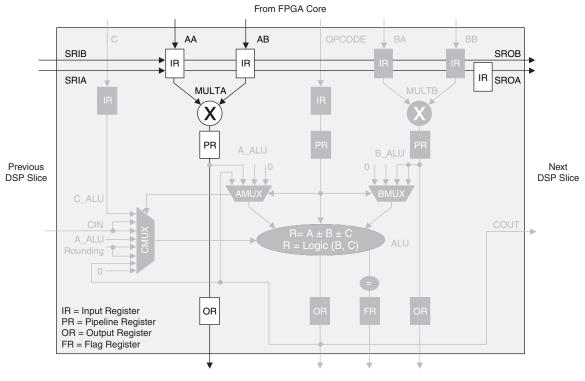

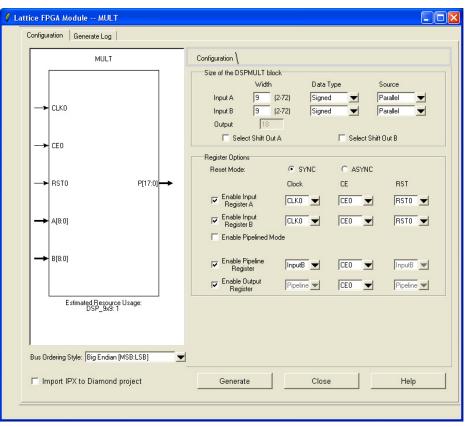

| MULT DSP Element                               |     |

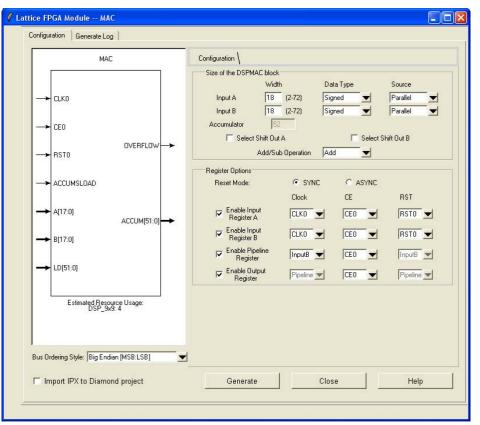

| MAC DSP Element                                |     |

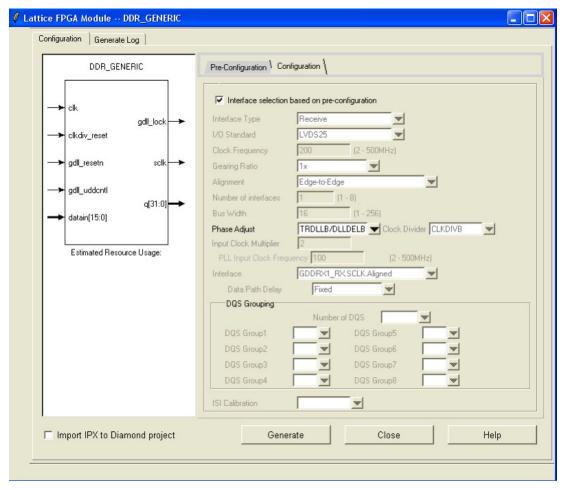

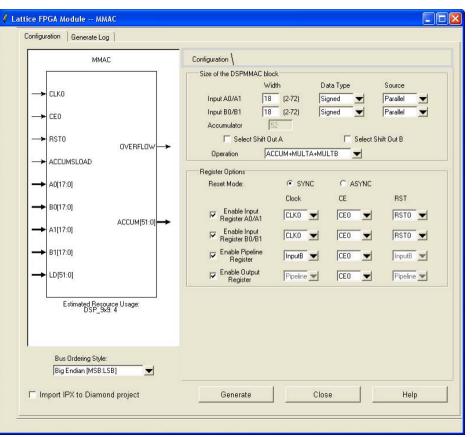

| MMAC DSP Element                               |     |

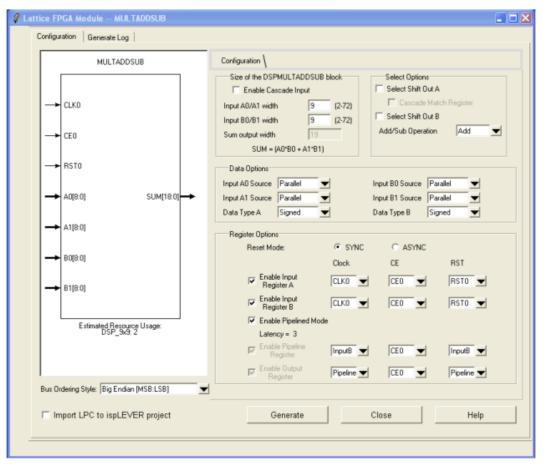

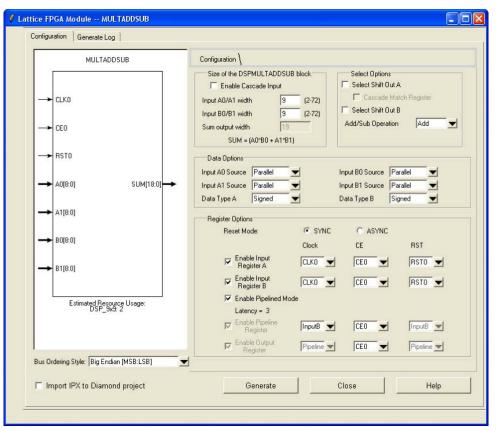

| MULTADDSUB DSP Element                         |     |

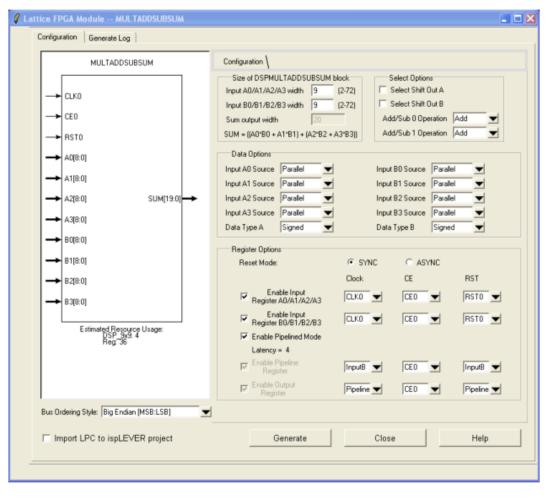

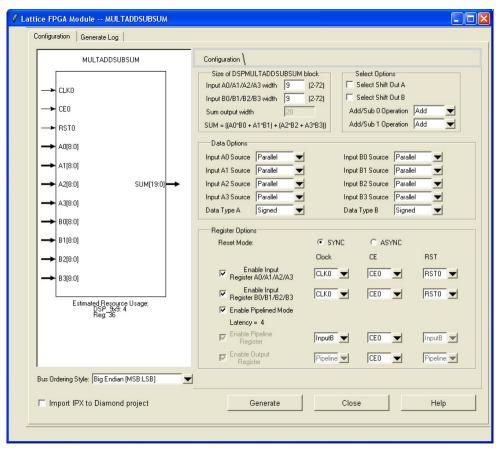

| MULTADDSUBSUM DSP Element                      |     |

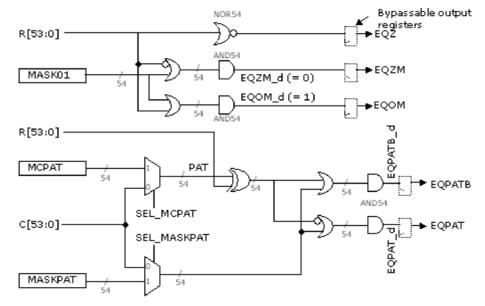

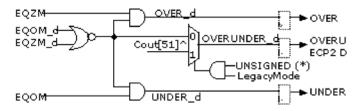

| Advanced sysDSP Slice Features                 |     |

| Cascading                                      |     |

| Addition                                       |     |

| Rounding                                       |     |

| ALU Flags                                      |     |

| Clock, Clock Enable and Reset Resources        |     |

| Resources Available in the LatticeECP3 Family  |     |

© 2013 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

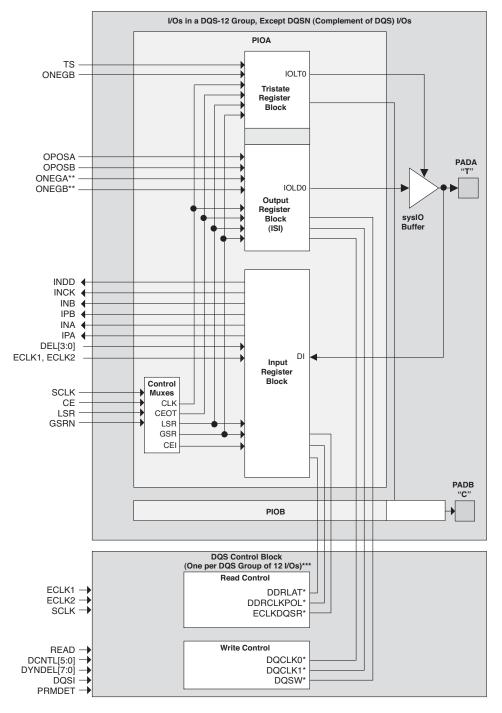

| Programmable I/O Cells (PIC)                      | 2-31 |

|---------------------------------------------------|------|

| PIO                                               | 2-32 |

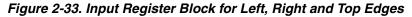

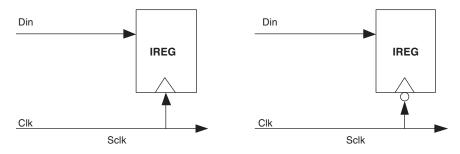

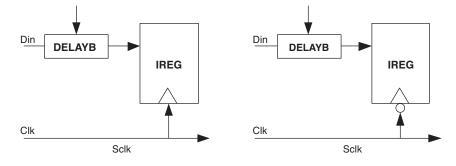

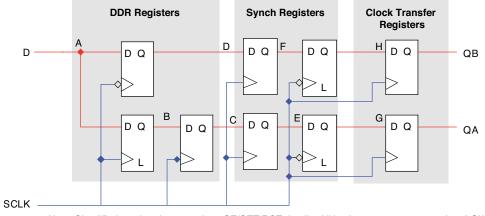

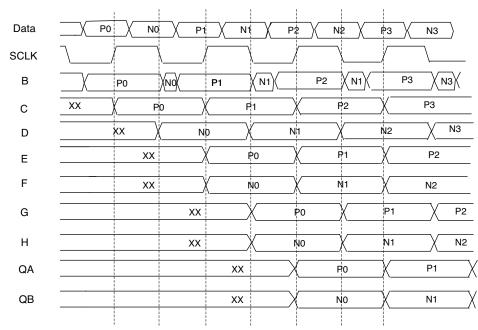

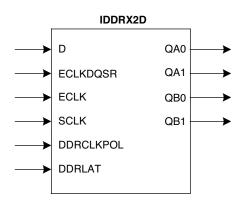

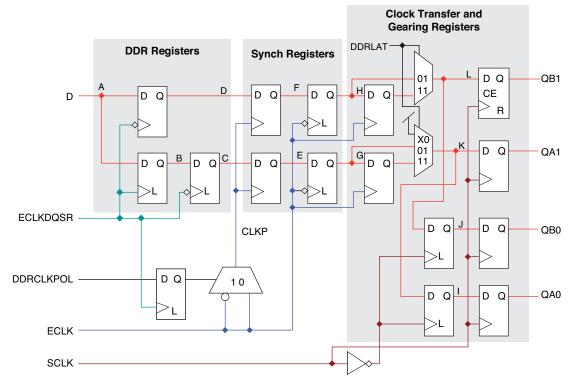

| Input Register Block                              | 2-32 |

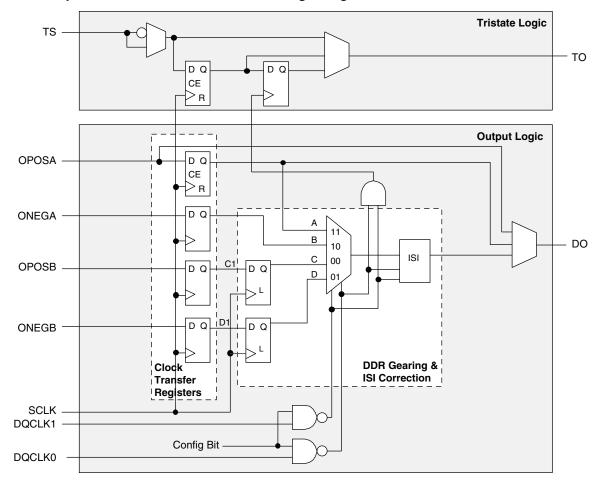

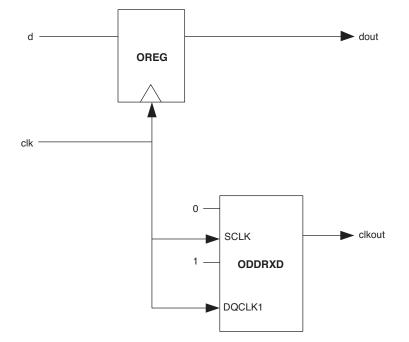

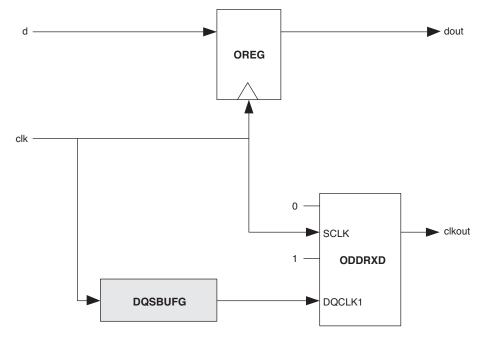

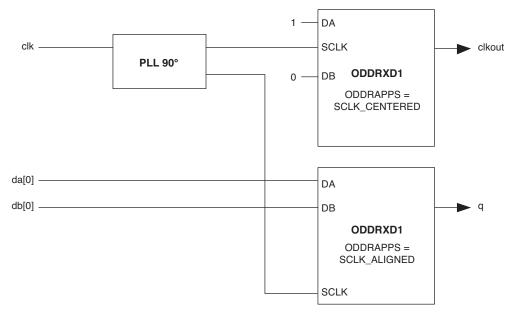

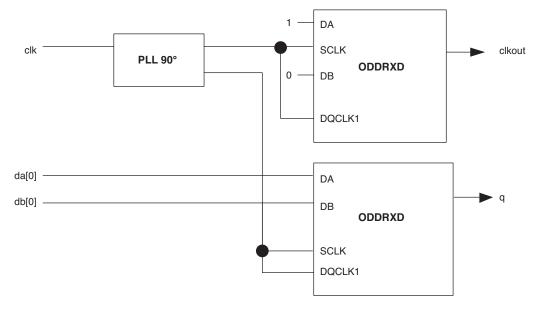

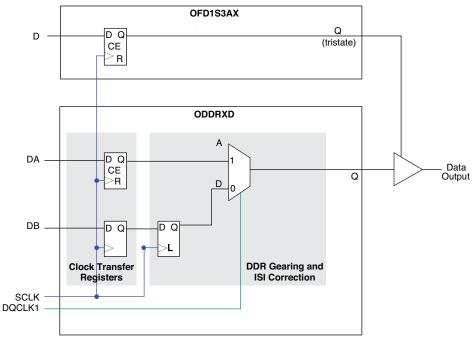

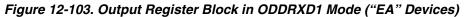

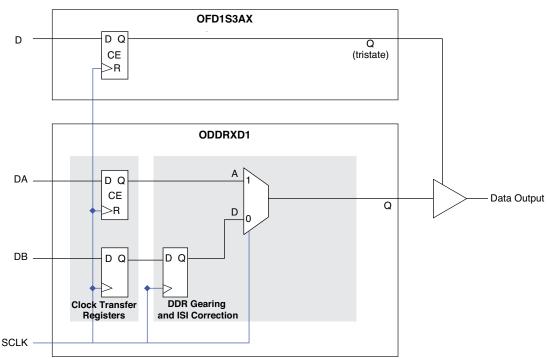

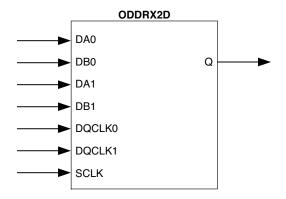

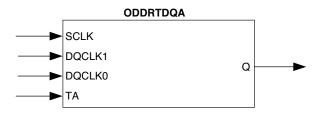

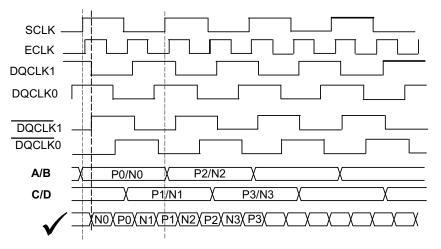

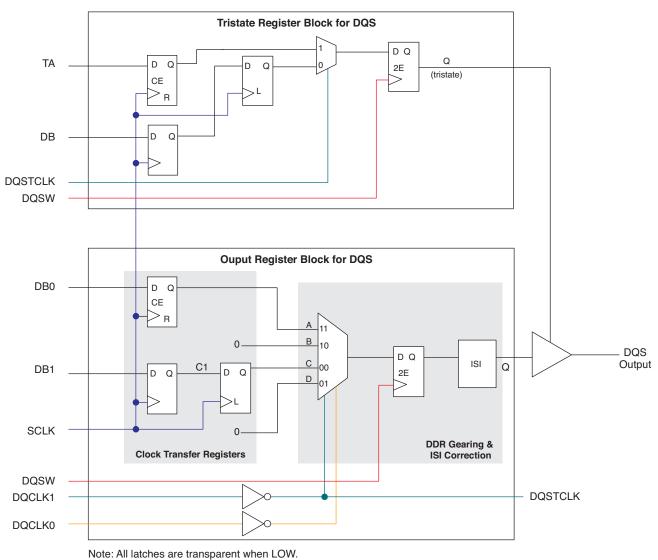

| Output Register Block                             | 2-34 |

| Tristate Register Block                           | 2-35 |

| ISI Calibration                                   | 2-35 |

| Control Logic Block                               | 2-36 |

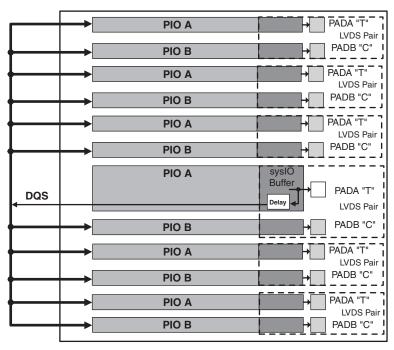

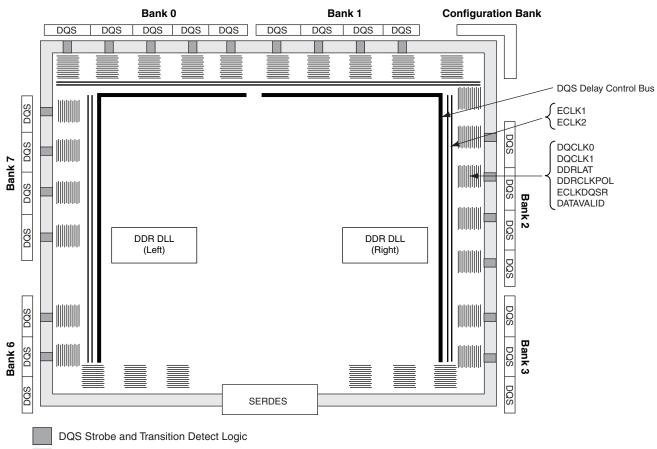

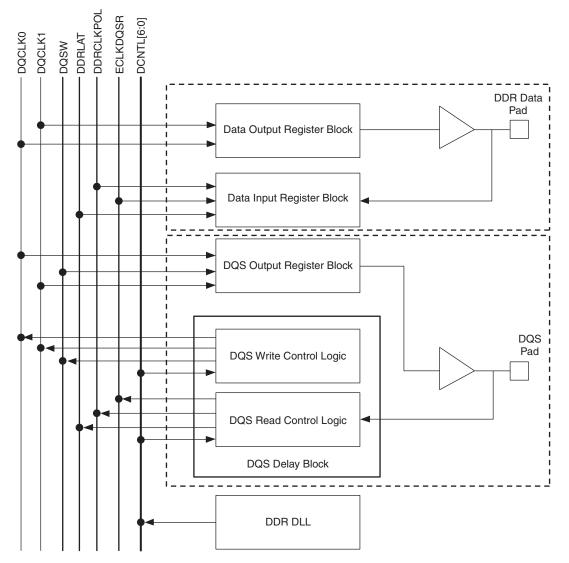

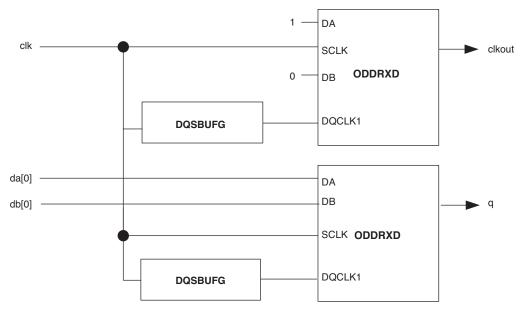

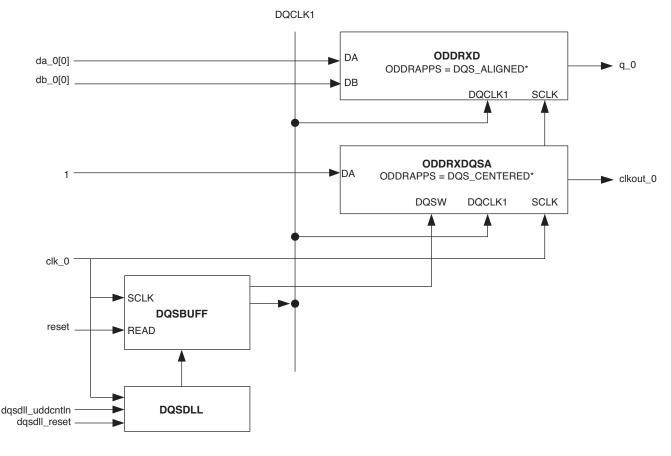

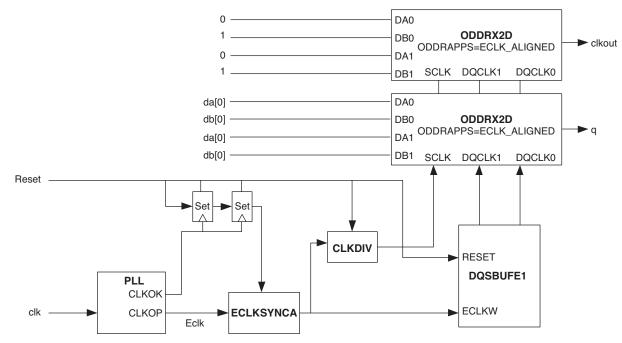

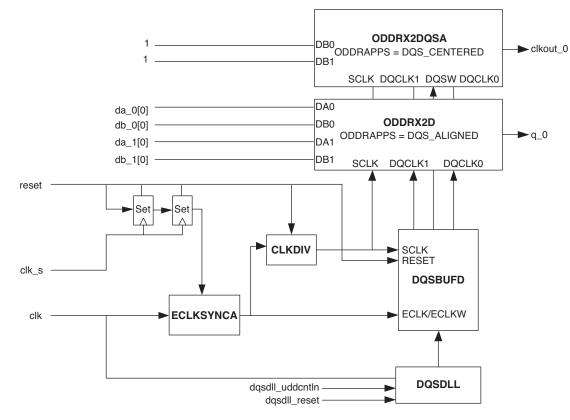

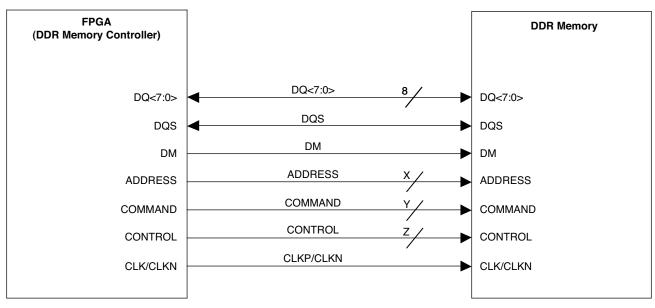

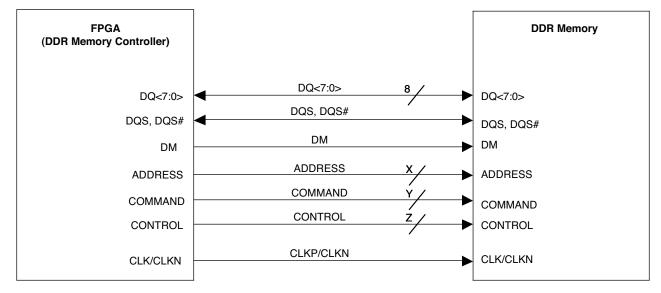

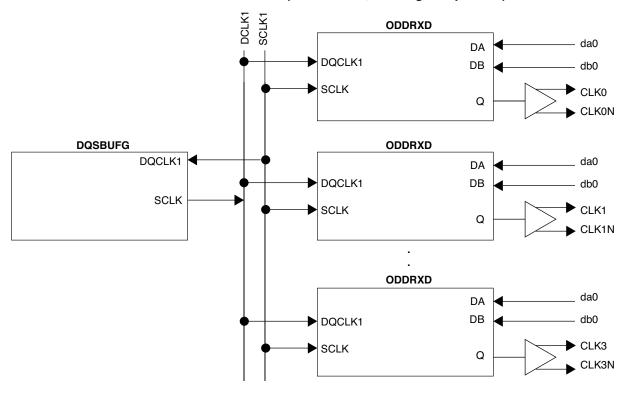

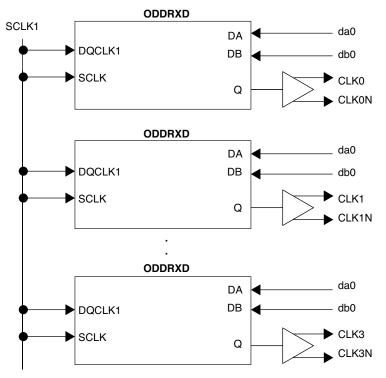

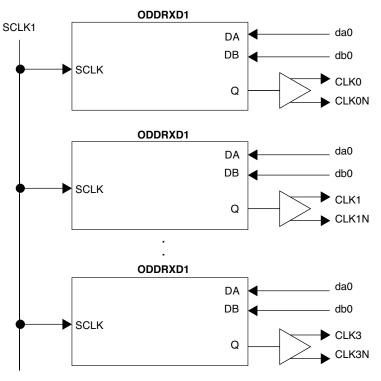

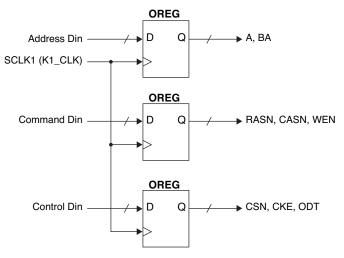

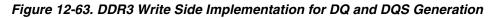

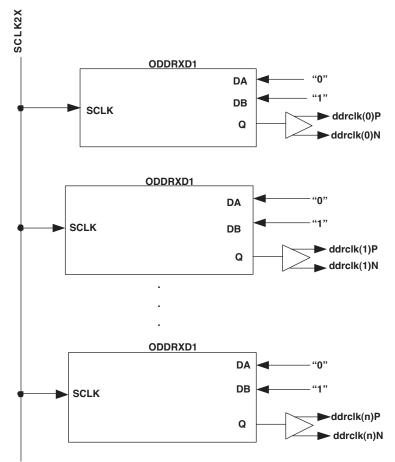

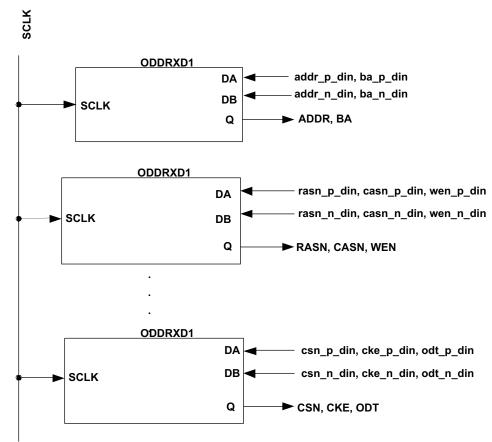

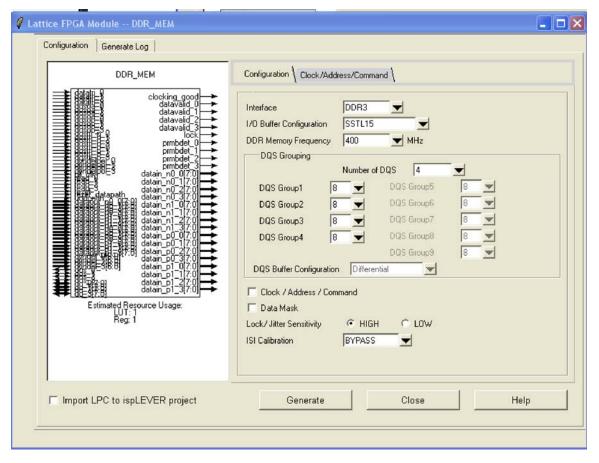

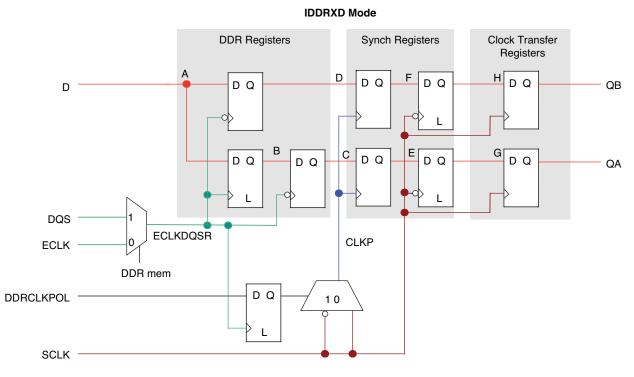

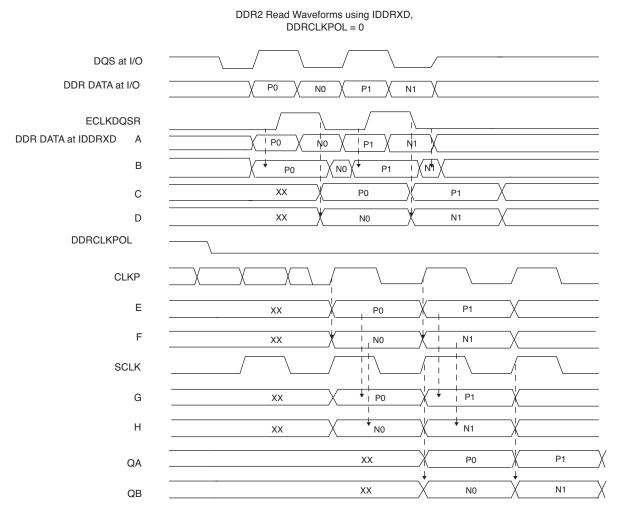

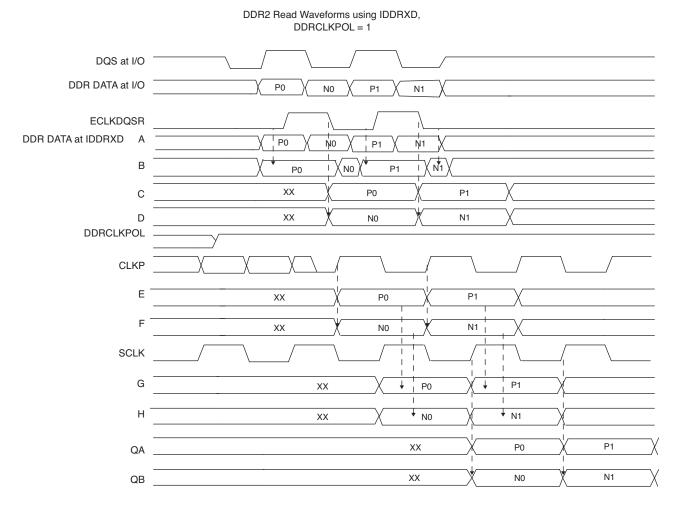

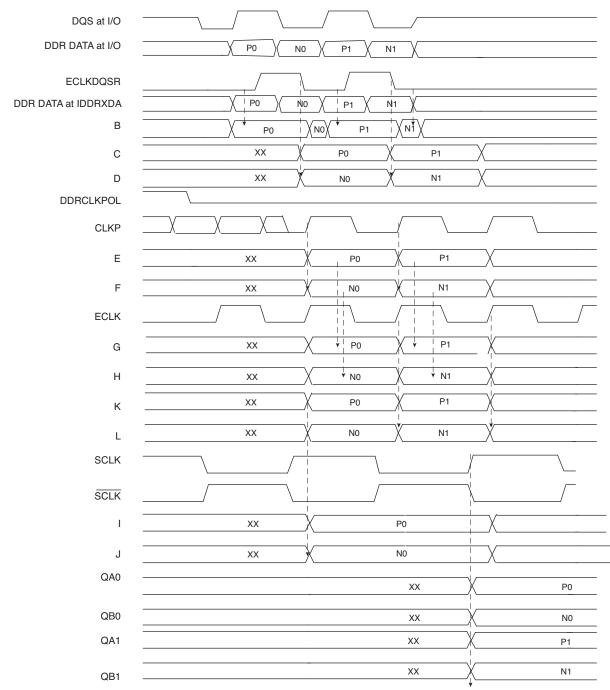

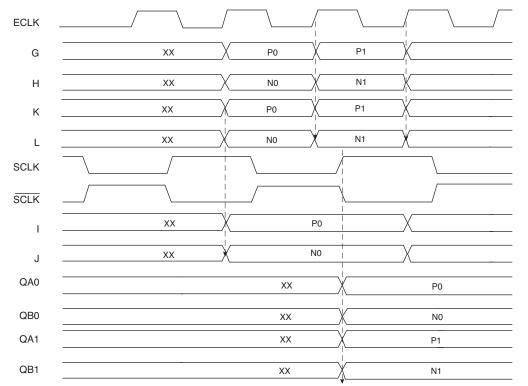

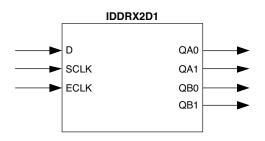

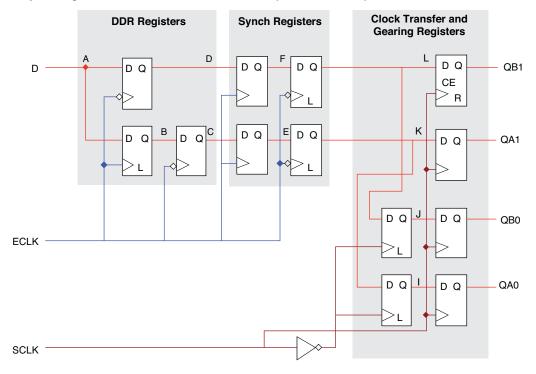

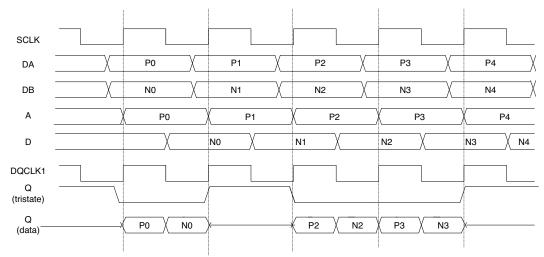

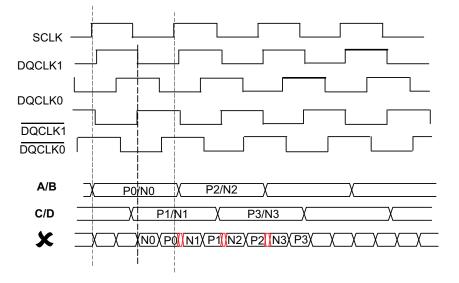

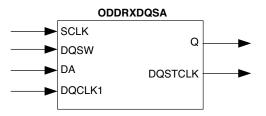

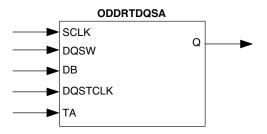

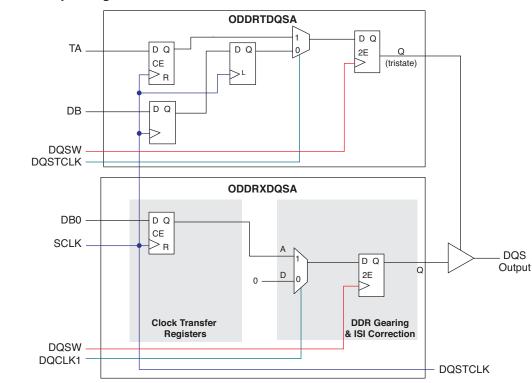

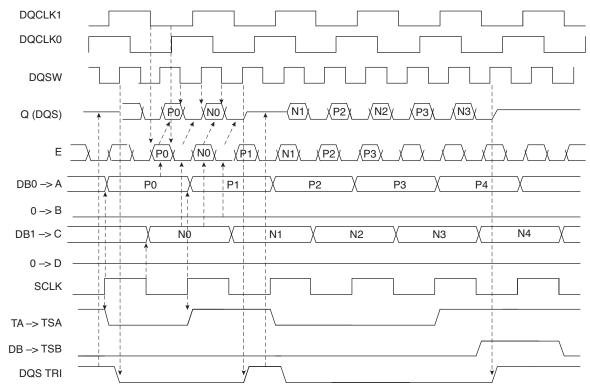

| DDR Memory Support                                | 2-36 |

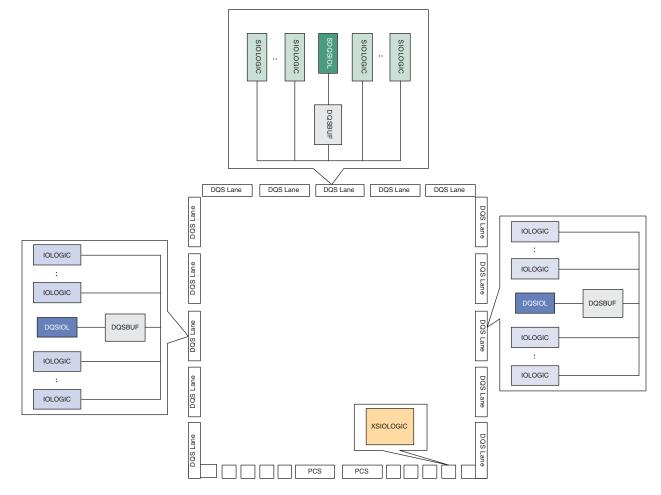

| Left and Right Edges                              | 2-36 |

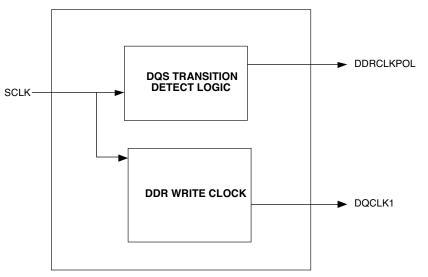

| Bottom Edge                                       | 2-36 |

| Top Edge.                                         | 2-36 |

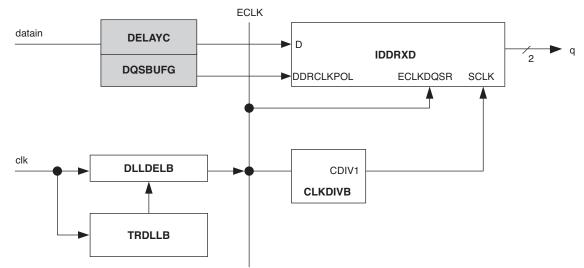

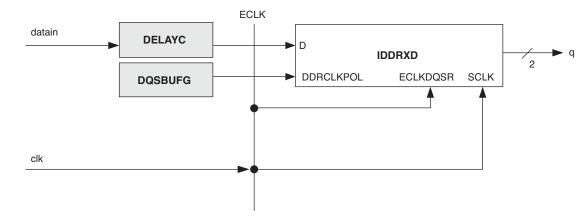

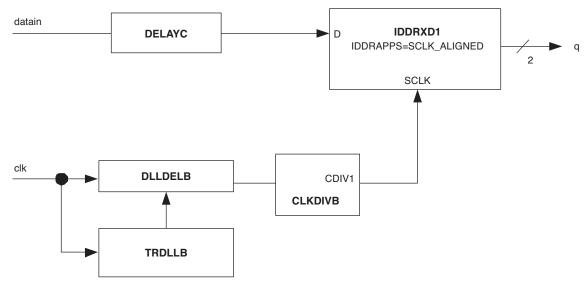

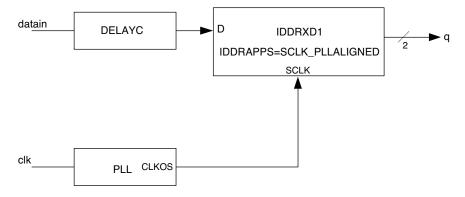

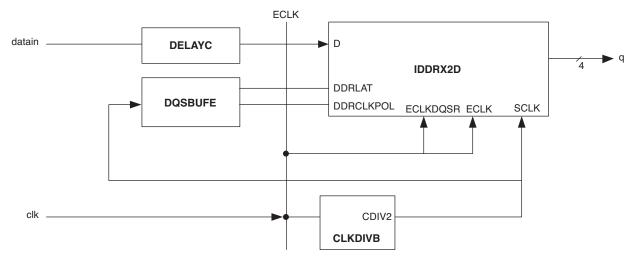

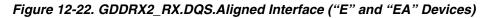

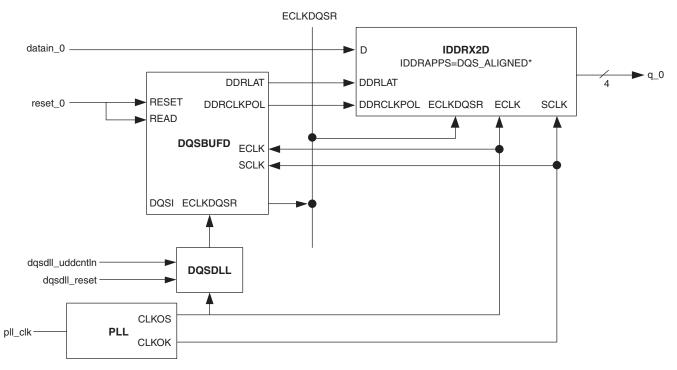

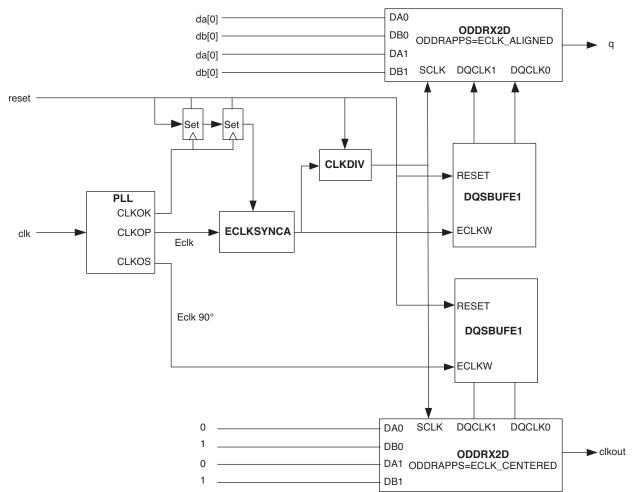

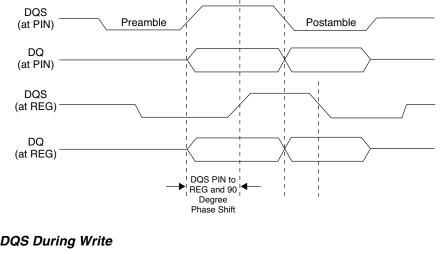

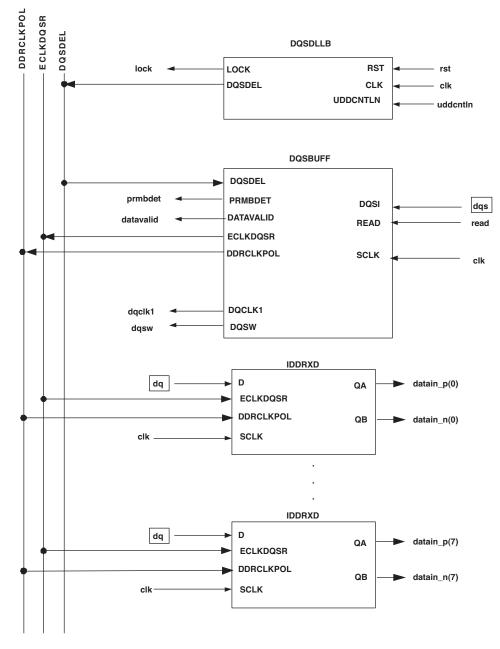

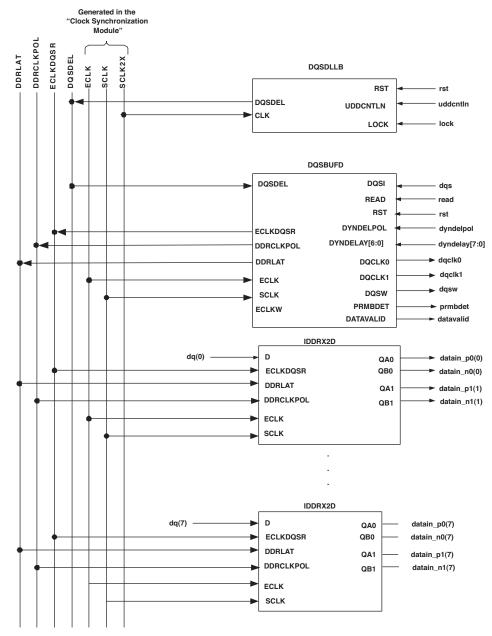

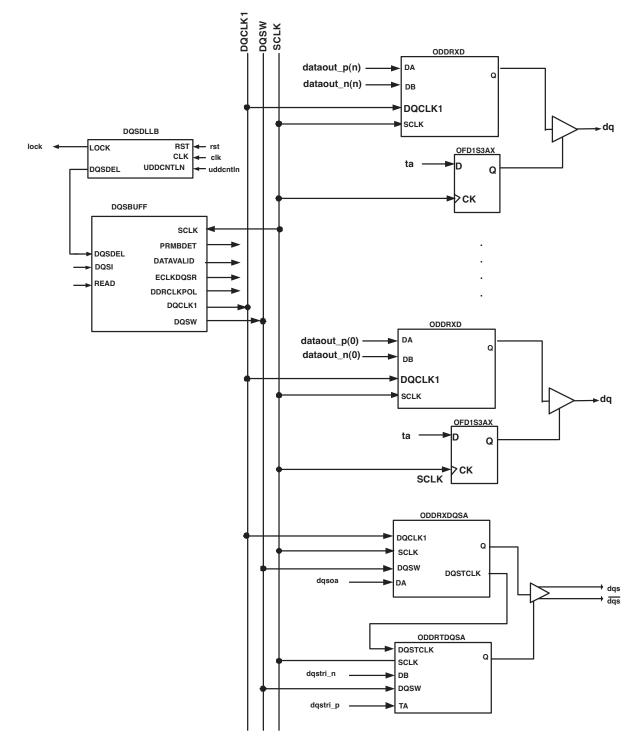

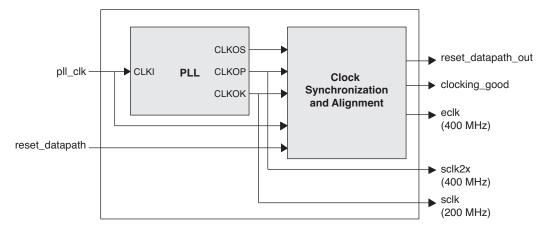

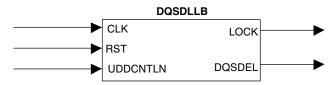

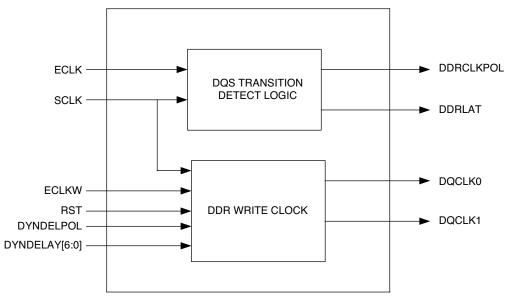

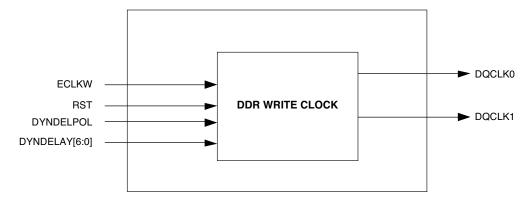

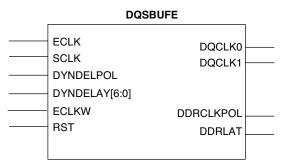

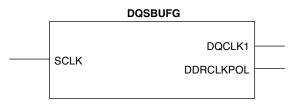

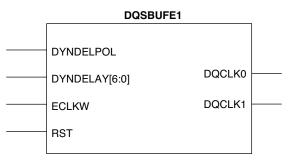

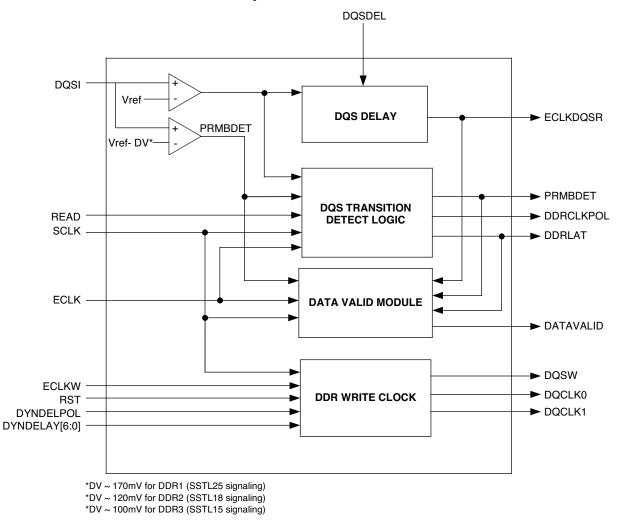

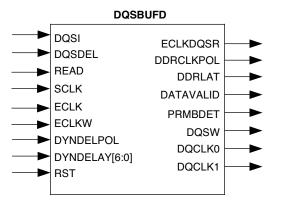

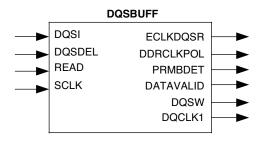

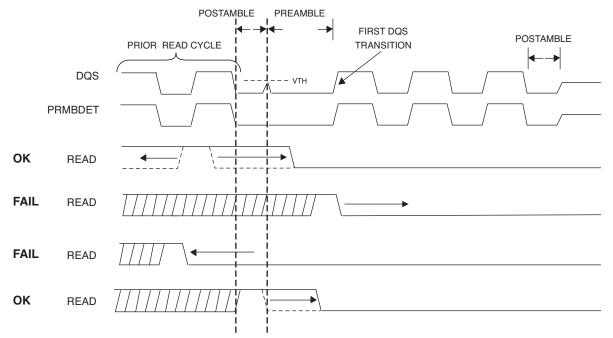

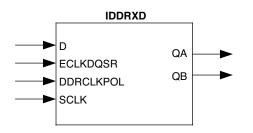

| DLL Calibrated DQS Delay Block                    | 2-36 |

| Polarity Control Logic                            | 2-39 |

| DDR3 Memory Support                               | 2-39 |

| sysI/O Buffer                                     | 2-40 |

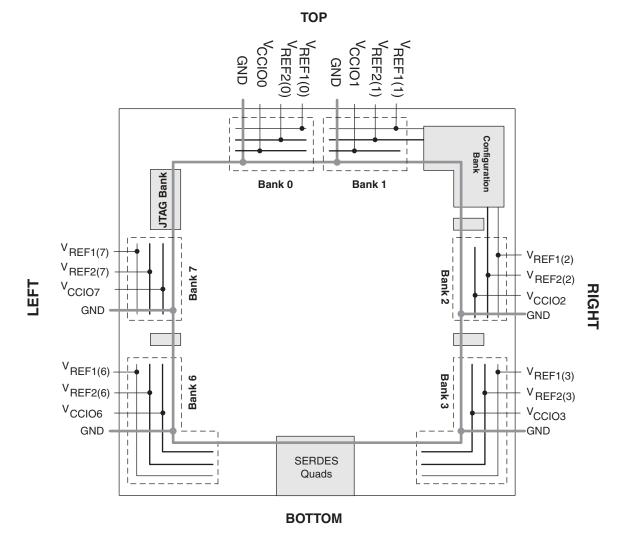

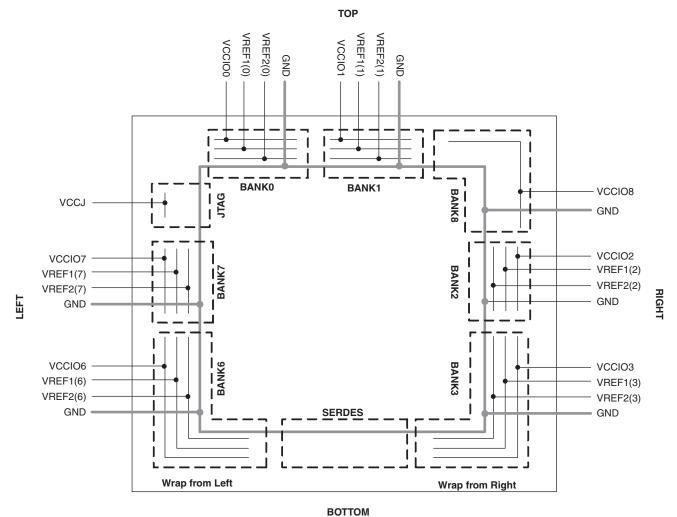

| sysI/O Buffer Banks                               | 2-40 |

| Typical sysI/O I/O Behavior During Power-up       | 2-42 |

| Supported sysI/O Standards                        | 2-42 |

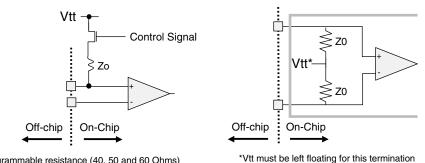

| On-Chip Programmable Termination                  |      |

| Equalization Filter                               |      |

| Hot Socketing                                     | 2-44 |

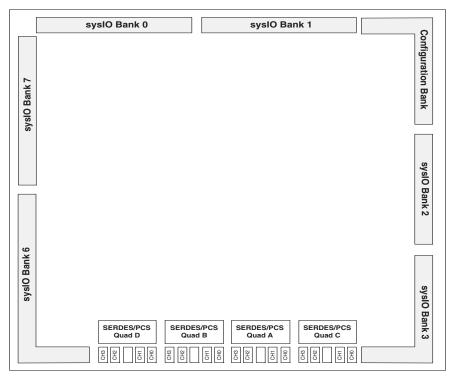

| SERDES and PCS (Physical Coding Sublayer)         | 2-44 |

| SERDES Block                                      |      |

| PCS                                               |      |

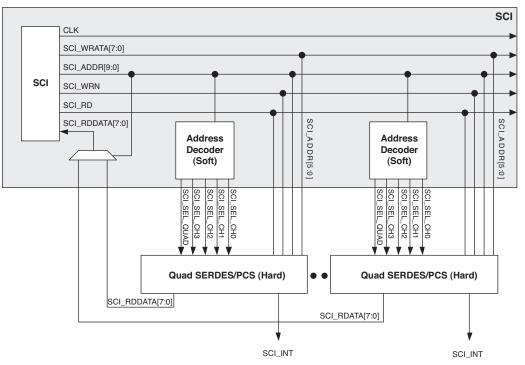

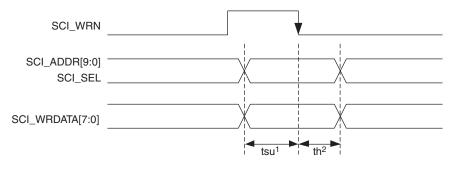

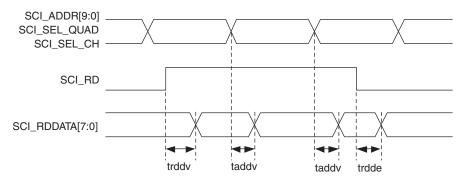

| SCI (SERDES Client Interface) Bus                 | 2-46 |

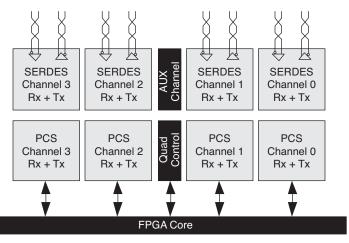

| Flexible Quad SERDES Architecture                 |      |

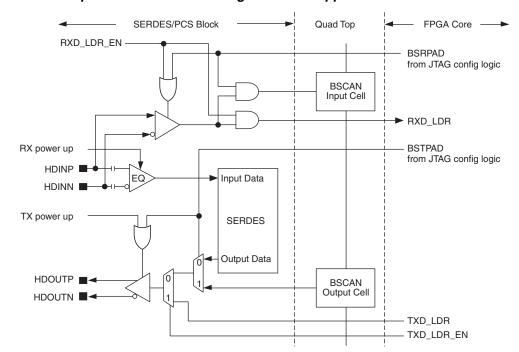

| IEEE 1149.1-Compliant Boundary Scan Testability   | 2-48 |

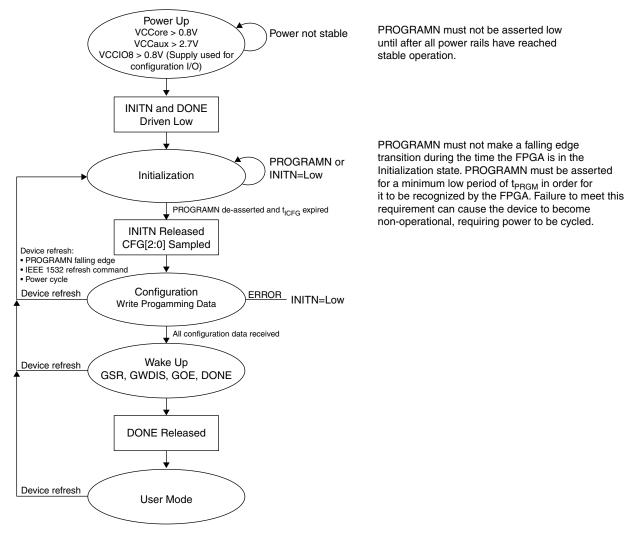

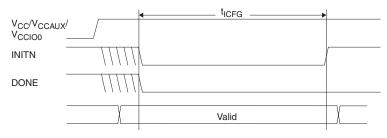

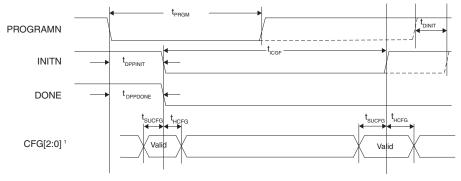

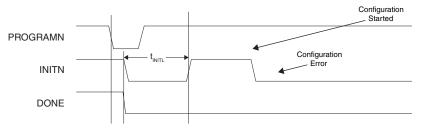

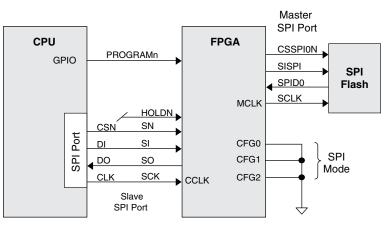

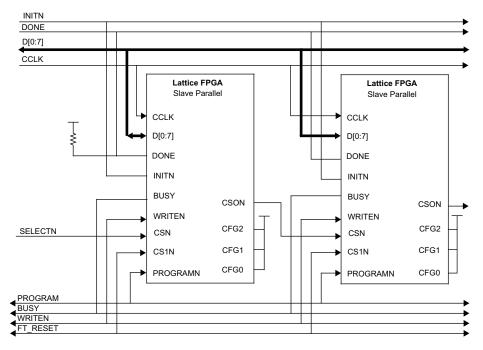

| Device Configuration                              | 2-48 |

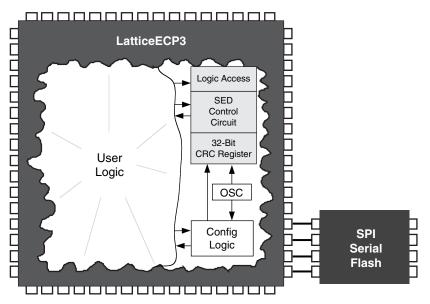

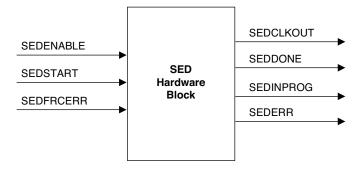

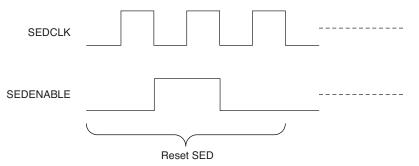

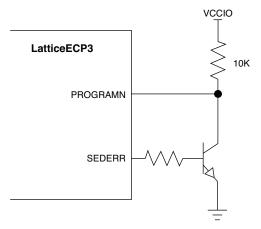

| Soft Error Detect (SED) Support                   | 2-49 |

| External Resistor                                 | 2-49 |

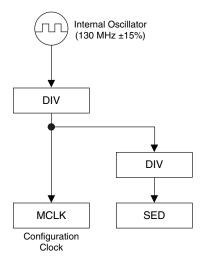

| On-Chip Oscillator                                | 2-49 |

| Density Shifting                                  | 2-50 |

| DC and Switching Characteristics                  |      |

| Absolute Maximum Ratings <sup>,</sup>             |      |

| Recommended Operating Conditions                  |      |

| Hot Socketing Specifications                      | 3-2  |

| Hot Socketing Requirements                        |      |

| ESD Performance                                   |      |

| DC Electrical Characteristics                     |      |

| LatticeECP3 Supply Current (Standby)              | 3-4  |

| SERDES Power Supply Requirements                  |      |

| sysI/O Recommended Operating Conditions           |      |

| sysI/O Single-Ended DC Electrical Characteristics |      |

| sysI/O Differential Electrical Characteristics    | 3-8  |

| LVDS25                                            |      |

| Differential HSTL and SSTL                        | 3-8  |

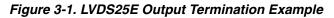

| LVDS25E                                           |      |

| LVCMOS33D                                         | 3-9  |

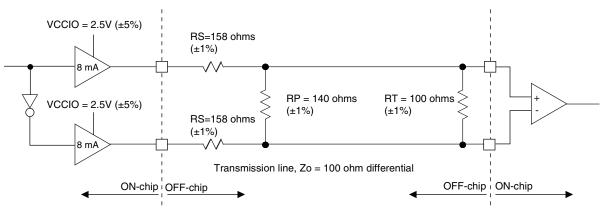

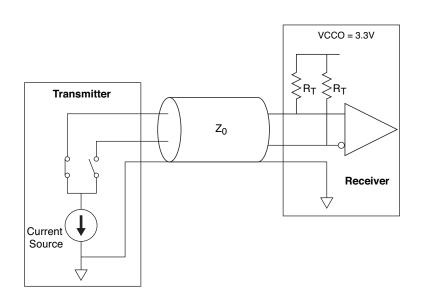

| BLVDS25                                           | 3-10 |

| LVPECL33                                          |      |

| RSDS25E                                           | 3-12 |

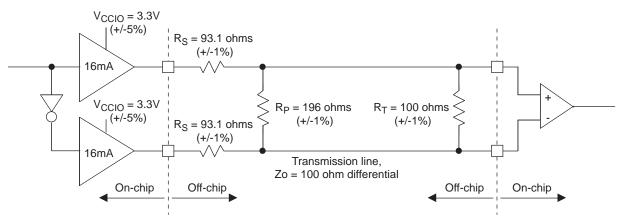

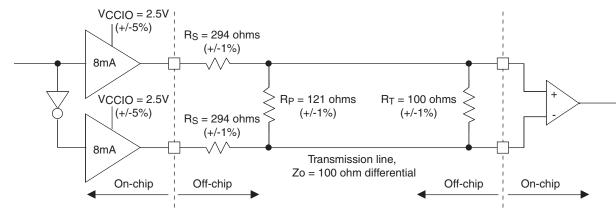

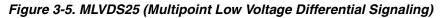

| MLVDS25                                           | 3-13 |

| Typical Building Block Function Performance       | 3-14 |

| Pin-to-Pin Performance (LVCMOS25 12mA Drive)      | 3-14 |

| Derating Timing Tables                                                                            | 3-15 |

|---------------------------------------------------------------------------------------------------|------|

| LatticeECP3 External Switching Characteristics                                                    |      |

| LatticeECP3 Internal Switching Characteristics                                                    | 3-25 |

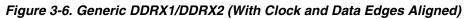

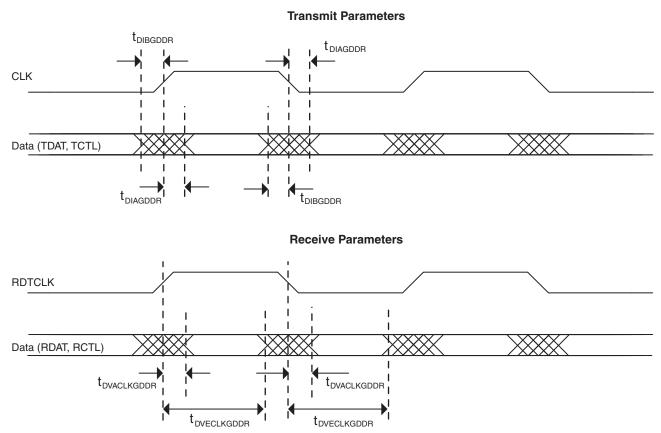

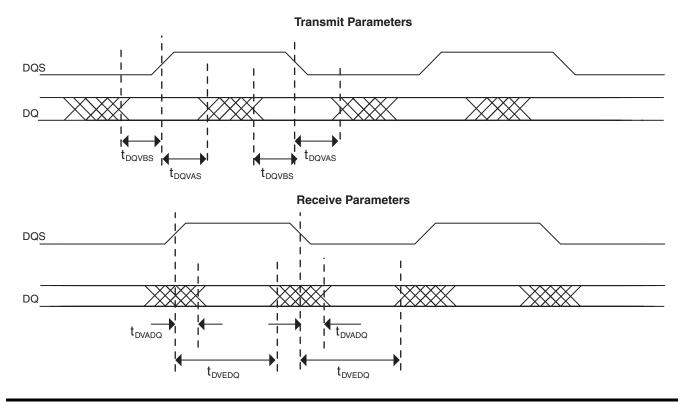

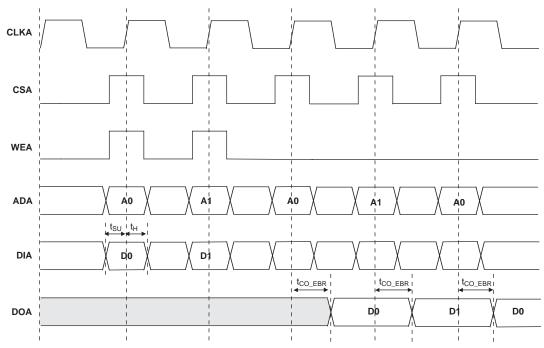

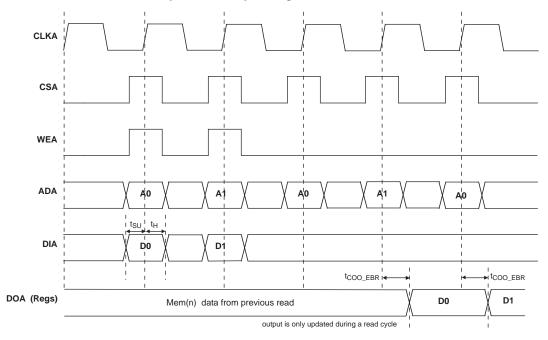

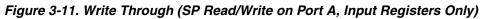

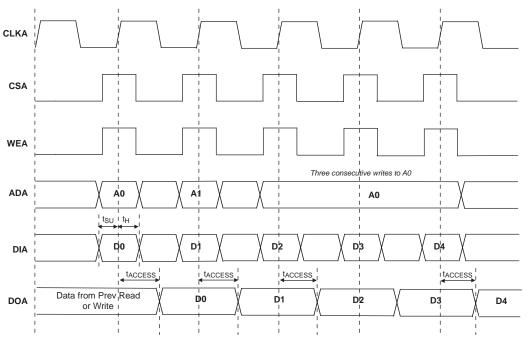

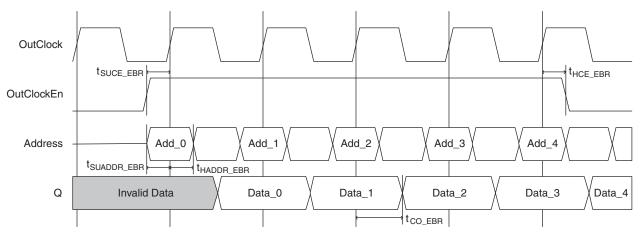

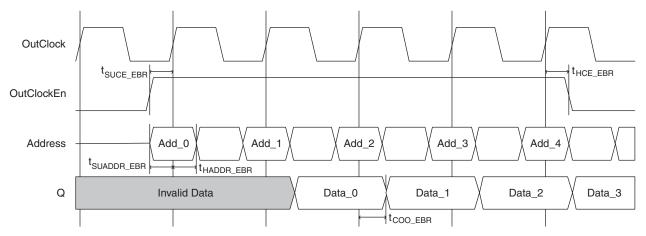

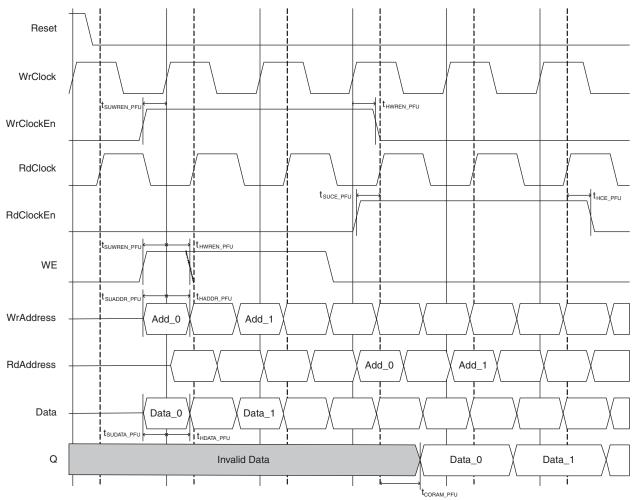

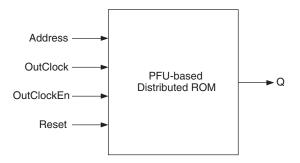

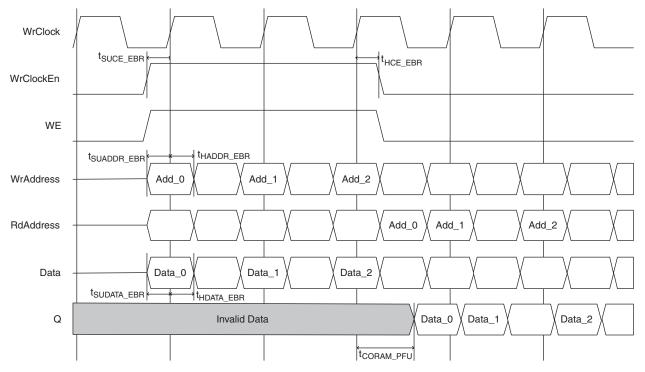

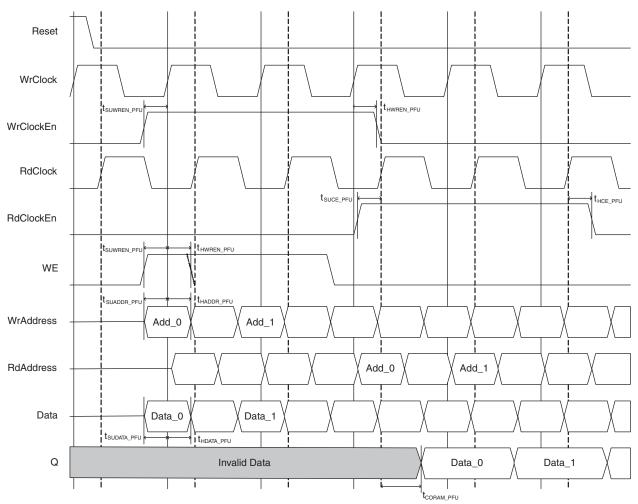

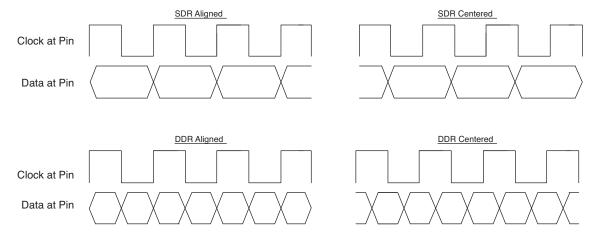

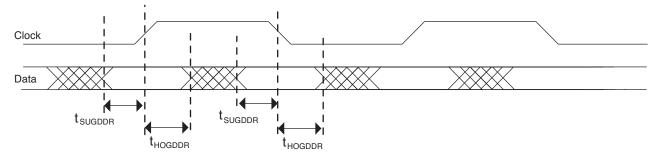

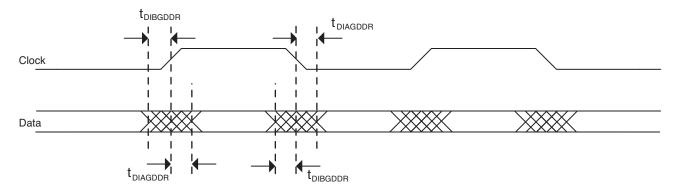

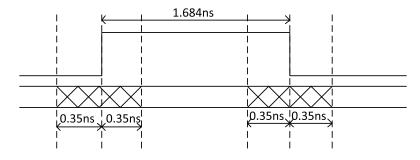

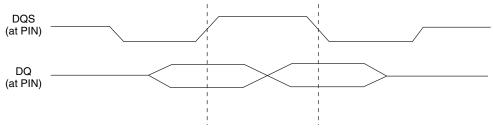

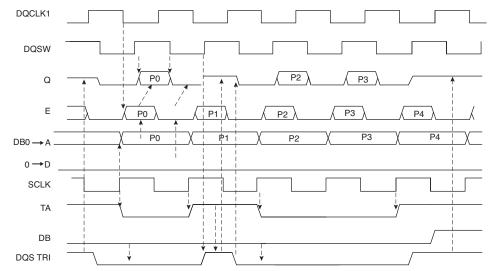

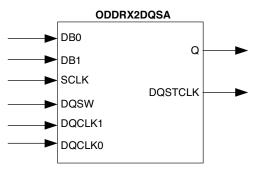

| Timing Diagrams                                                                                   | 3-27 |

| LatticeECP3 Family Timing Adders                                                                  | 3-29 |

| LatticeECP3 Maximum I/O Buffer Speed                                                              | 3-32 |

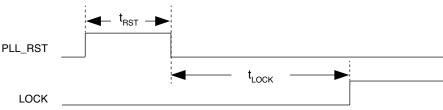

| sysCLOCK PLL Timing                                                                               | 3-34 |

| DLL Timing                                                                                        | 3-35 |

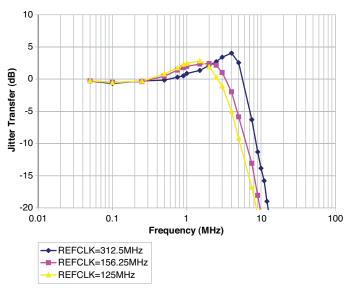

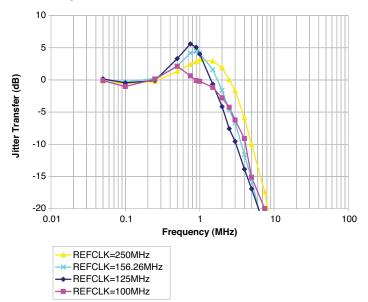

| SERDES High-Speed Data Transmitter                                                                | 3-36 |

| SERDES/PCS Block Latency                                                                          | 3-38 |

| SERDES High Speed Data Receiver                                                                   | 3-39 |

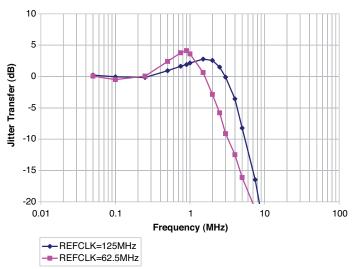

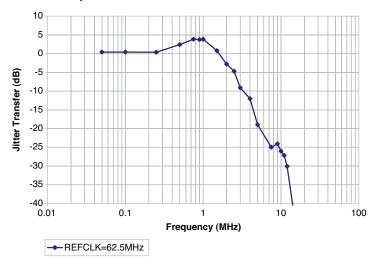

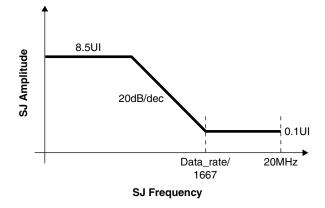

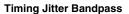

| Input Data Jitter Tolerance                                                                       |      |

| SERDES External Reference Clock                                                                   | 3-41 |

| PCI Express Electrical and Timing Characteristics                                                 | 3-44 |

| AC and DC Characteristics                                                                         | 3-44 |

| XAUI/Serial Rapid I/O Type 3/CPRI LV E.30 Electrical and Timing                                   |      |

| Characteristics                                                                                   |      |

| AC and DC Characteristics                                                                         |      |

| Serial Rapid I/O Type 2/CPRI LV E.24 Electrical and Timing Characteristics                        | 3-47 |

| AC and DC Characteristics                                                                         |      |

| Gigabit Ethernet/Serial Rapid I/O Type 1/SGMII/CPRI LV E.12 Electrical and Timing Characteristics | 3-48 |

| AC and DC Characteristics                                                                         |      |

| SMPTE SD/HD-SDI/3G-SDI (Serial Digital Interface) Electrical and Timing Characteristics           | 3-49 |

| AC and DC Characteristics                                                                         | 3-49 |

| HDMI (High-Definition Multimedia Interface) Electrical and Timing                                 |      |

| Characteristics                                                                                   |      |

| AC and DC Characteristics                                                                         | 3-50 |

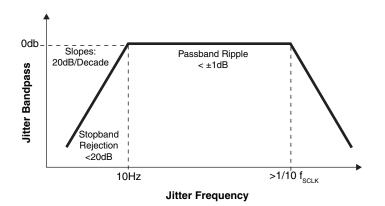

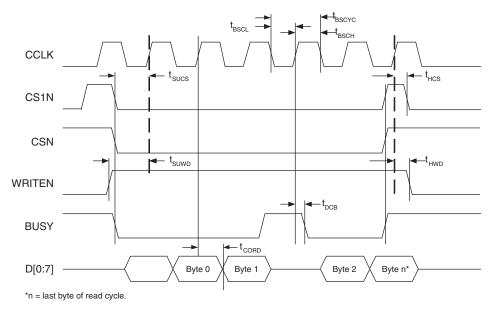

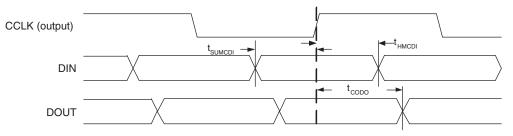

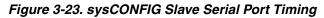

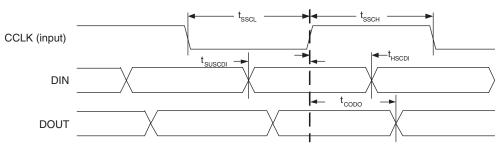

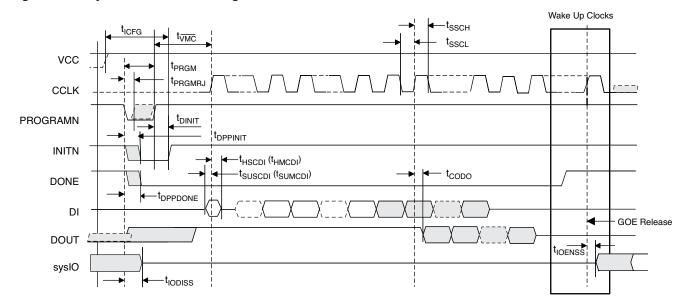

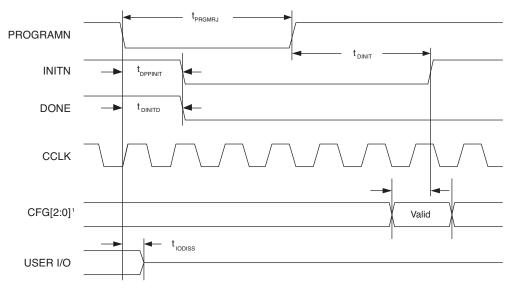

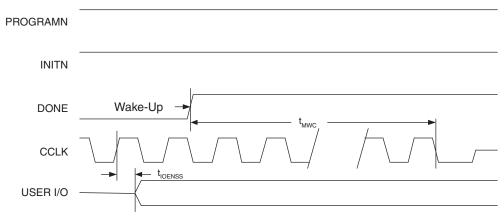

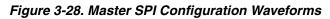

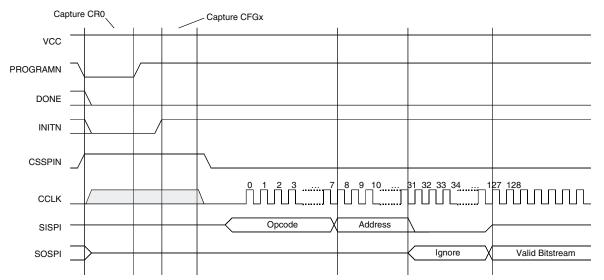

| LatticeECP3 sysCONFIG Port Timing Specifications                                                  |      |

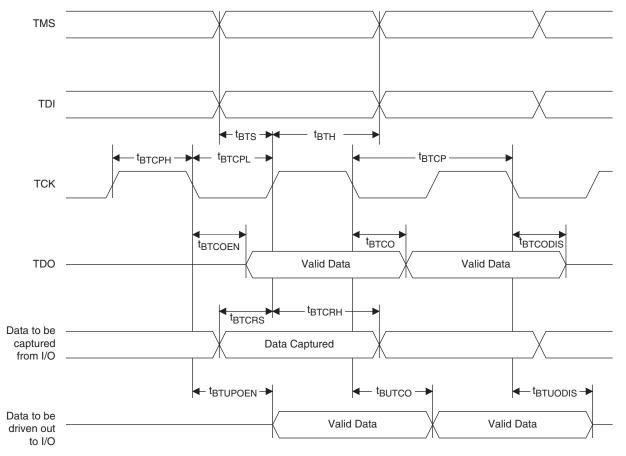

| JTAG Port Timing Specifications                                                                   | 3-58 |

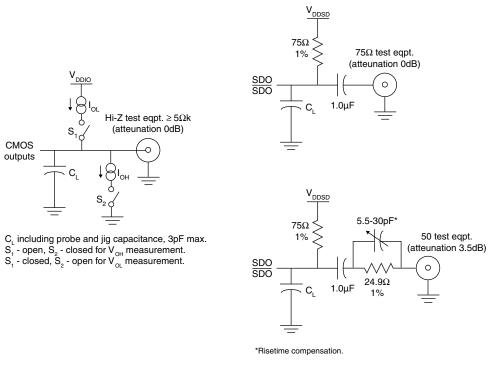

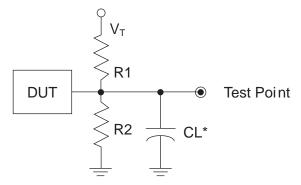

| Switching Test Conditions                                                                         | 3-59 |

| sysl/O Differential Electrical Characteristics                                                    |      |

| Transition Reduced LVDS (TRLVDS DC Specification)                                                 | 3-60 |

| Mini LVDS                                                                                         |      |

| Point-to-Point LVDS (PPLVDS)                                                                      |      |

| RSDS                                                                                              | 3-61 |

| Pinout Information                                                                                |      |

| Signal Descriptions                                                                               | 4-1  |

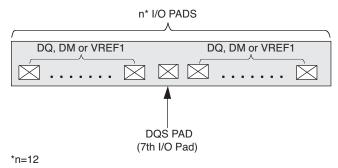

| PICs and DDR Data (DQ) Pins Associated with the DDR Strobe (DQS) Pin                              |      |

| Pin Information Summary (Cont.)                                                                   |      |

| Pin Information Summary (Cont.)                                                                   |      |

| Pin Information Summary (Cont.)                                                                   |      |

| Package Pinout Information                                                                        |      |

| Thermal Management                                                                                |      |

| For Further Information                                                                           | 4-10 |

| Ordering Information                                                                              |      |

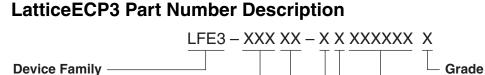

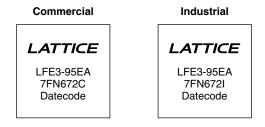

| LatticeECP3 Part Number Description                                                               |      |

| Ordering Information                                                                              |      |

| LatticeECP3 Devices, Green and Lead-Free Packaging                                                | 5-2  |

| Supplemental Information<br>For Further Information                                               | 6-1  |

| Revision History                                                                                  |      |

## Section II. LatticeECP3 Family Technical Notes LatticeECP3 SERDES/PCS Usage Guide

| Introduction                                                    | 8-1  |

|-----------------------------------------------------------------|------|

| Features                                                        | 8-1  |

| New Features Over LatticeECP2M™ SERDES/PCS                      | 8-1  |

| Using This Technical Note                                       | 8-2  |

| Standards Supported                                             | 8-2  |

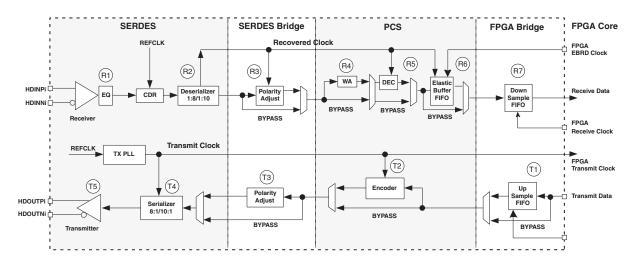

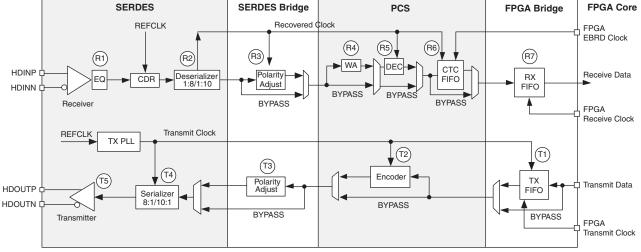

| Architecture Overview                                           | 8-3  |

| PCS Quads and Channels                                          |      |

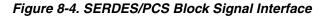

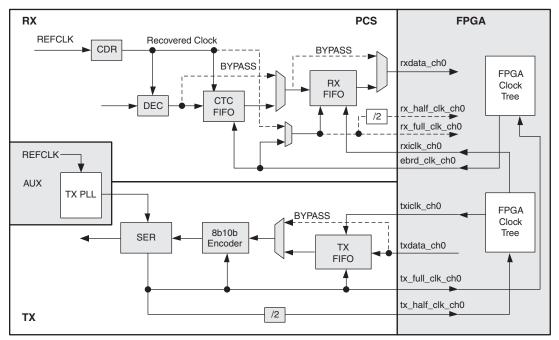

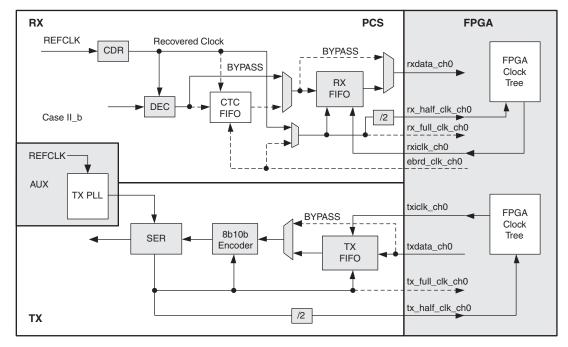

| Per Channel SERDES/PCS and FPGA Interface Ports                 | 8-4  |

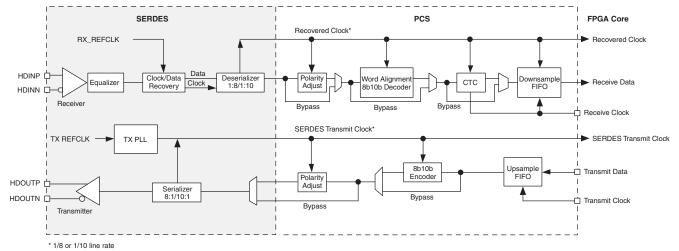

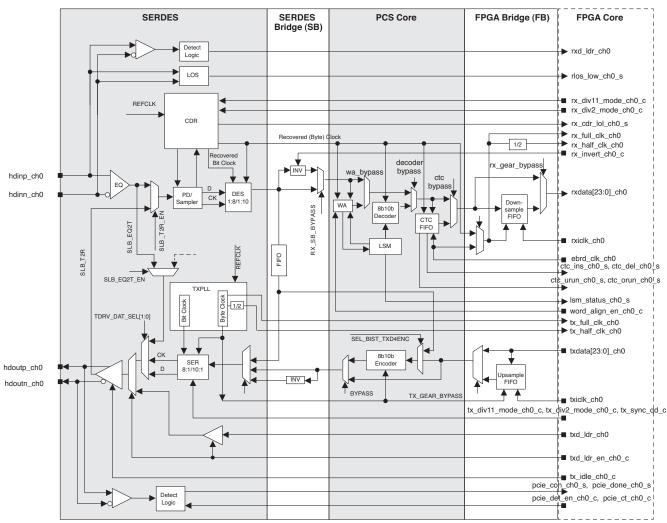

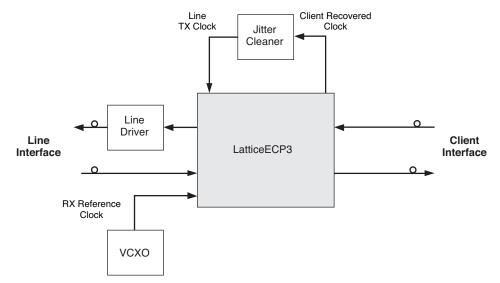

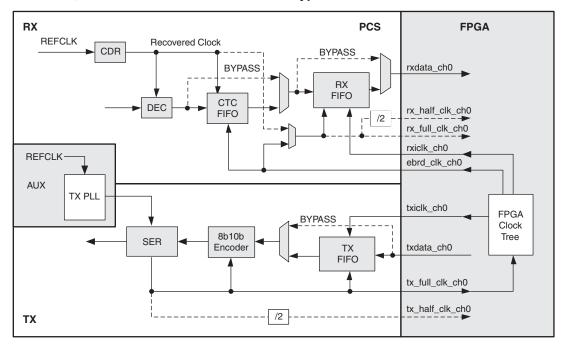

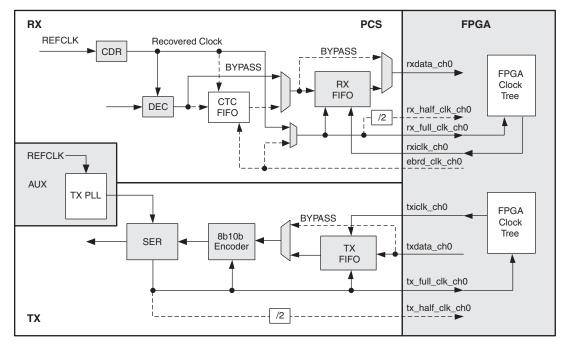

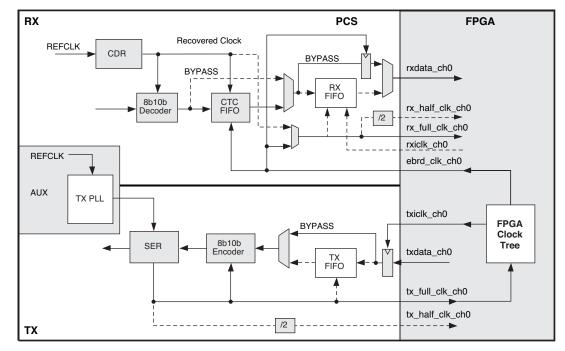

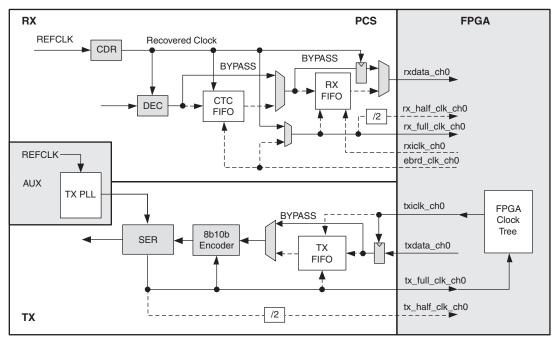

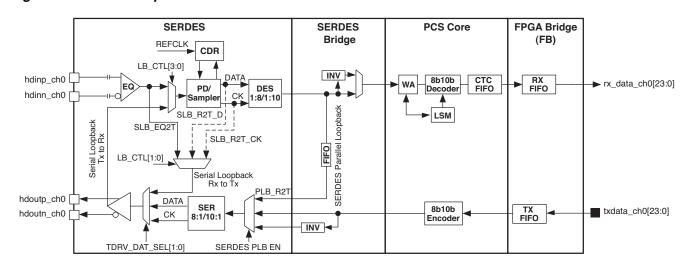

| Detailed Channel Block Diagram                                  | 8-5  |

| Clocks and Resets                                               | 8-6  |

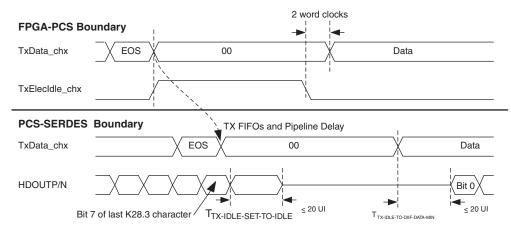

| Transmit Data Bus                                               | 8-6  |

| Receive Data Bus                                                | 8-7  |

| Mode-Specific Control/Status Signal Descriptions                |      |

| SERDES/PCS                                                      | 8-9  |

| I/O Descriptions                                                |      |

| SERDES/PCS Functional Description                               | 8-13 |

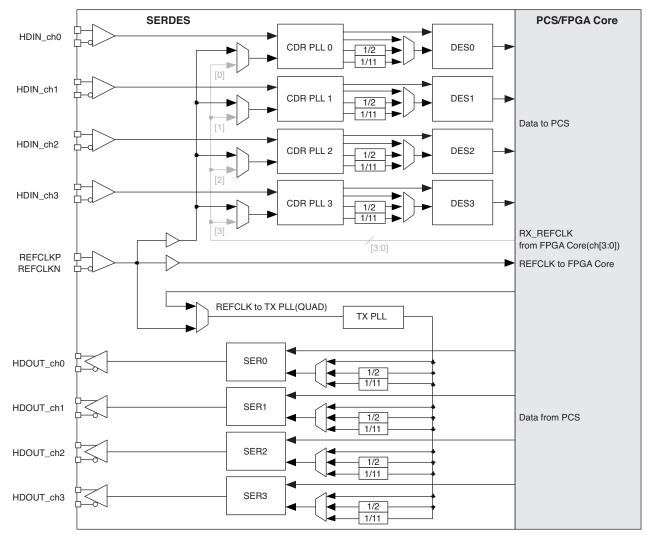

| SERDES                                                          | 8-13 |

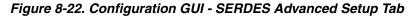

| Equalizer                                                       | 8-13 |

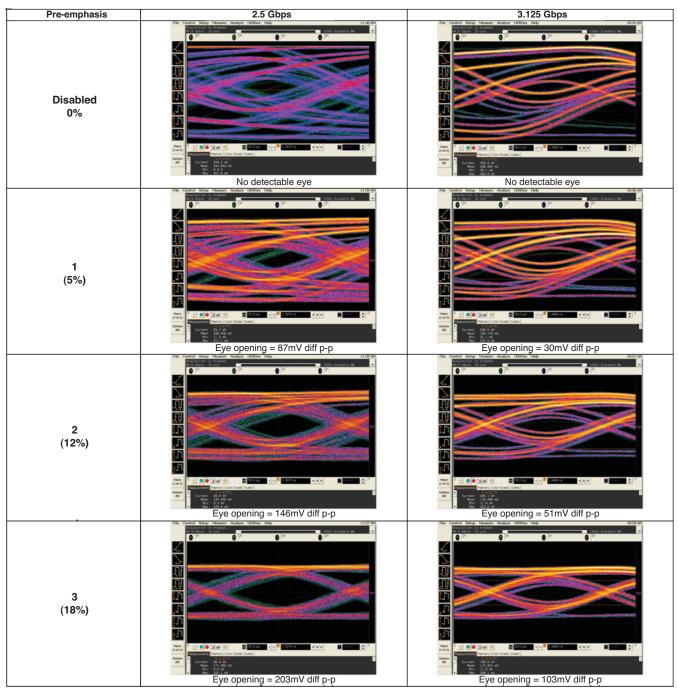

| Pre-Emphasis                                                    | 8-13 |

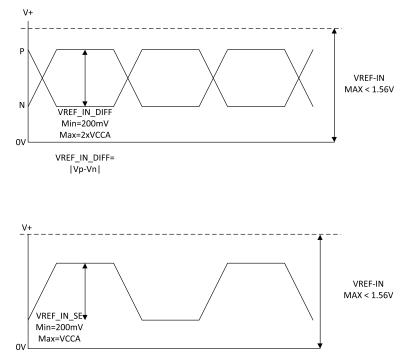

| Reference Clocks                                                |      |

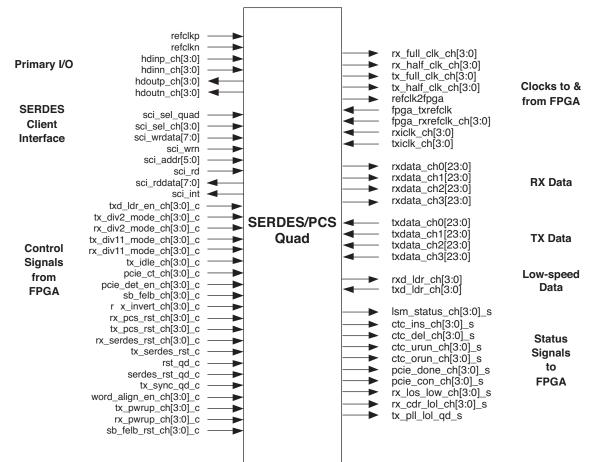

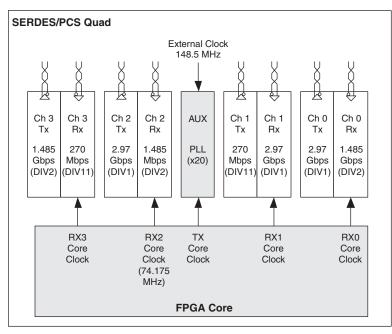

| SERDES Clock Architecture                                       |      |

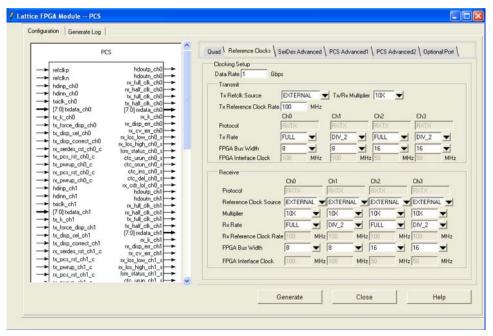

| Rate Modes                                                      |      |

| Reference Clock from an FPGA Core                               | 8-16 |

| Full Data, Div 2 and Div 11 Data Rates                          | 8-17 |

| Dynamic Switching Between Full Rate and Half Rate (DIV2)        | 8-18 |

| Reference Clock Sources                                         |      |

| Spread Spectrum Clocking (SSC) Support                          | 8-18 |

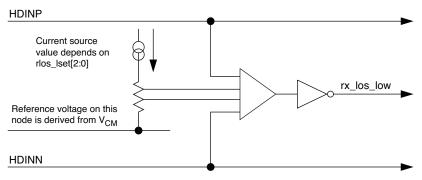

| Loss of Signal                                                  |      |

| Loss Of Lock                                                    |      |

| TX Lane-to-Lane Skew                                            | 8-19 |

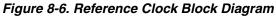

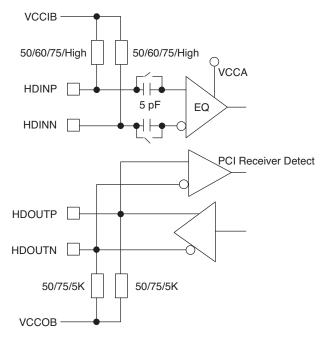

| SERDES PCS Configuration Setup                                  | 8-20 |

| Auto-Configuration File                                         |      |

| Transmit Data                                                   |      |

| Receive Data                                                    | 8-20 |

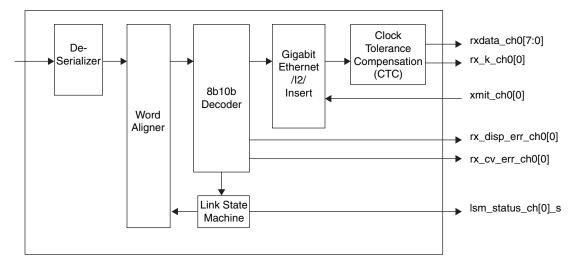

| 8b10b Decoder                                                   | 8-21 |

| External Link State Machine Option                              |      |

| Idle Insert for Gigabit Ethernet Mode                           |      |

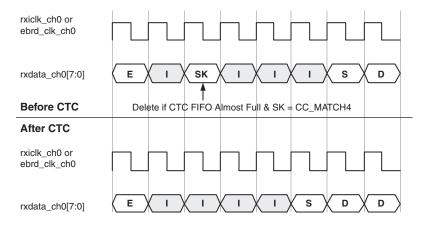

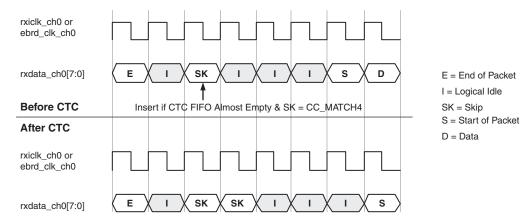

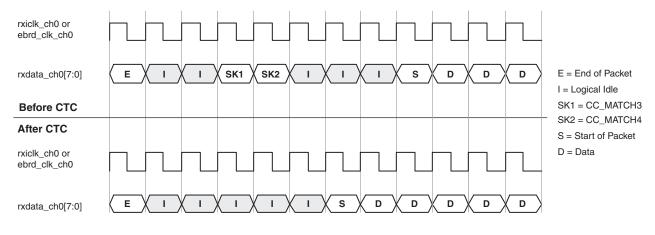

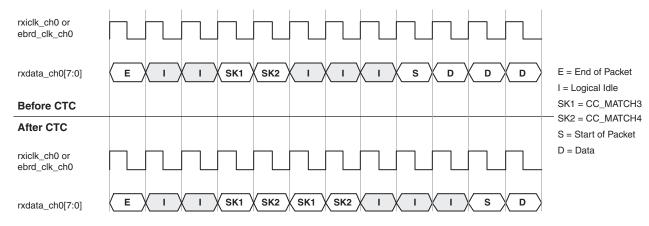

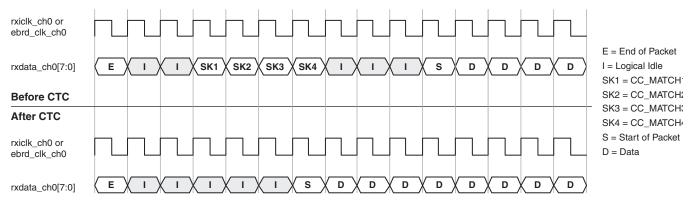

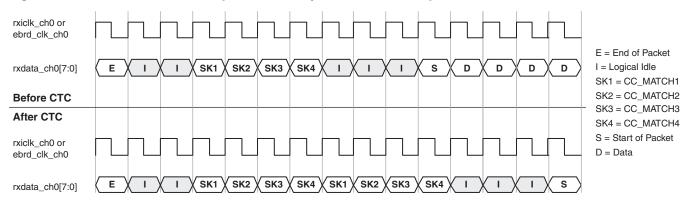

| Clock Tolerance Compensation                                    |      |

| Calculating Minimum Interpacket Gap                             |      |

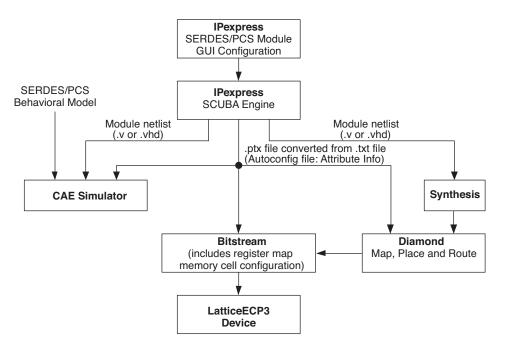

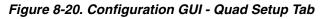

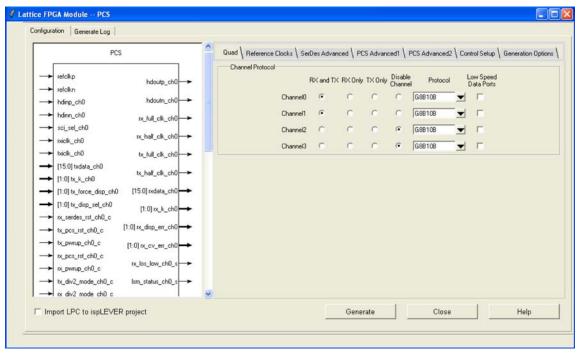

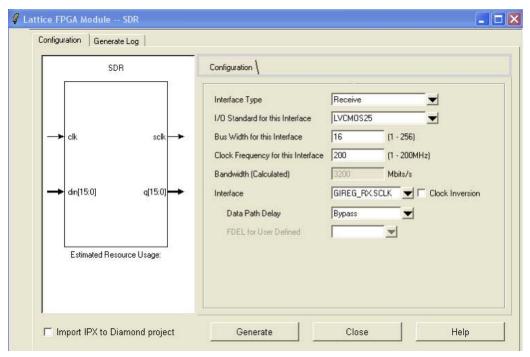

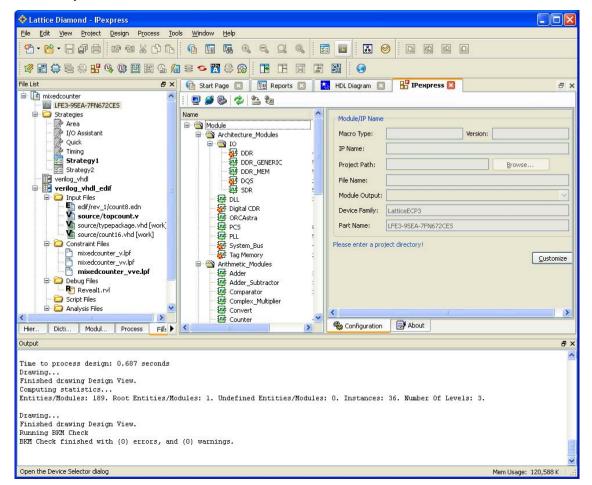

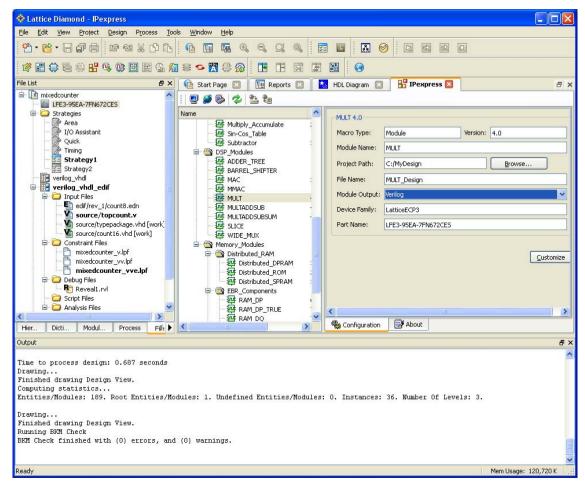

| PCS Module Generation in IPexpress                              |      |

| 8-Bit and 10-Bit SERDES-Only Modes                              | 8-40 |

| Generic 8b10b Mode                                              |      |

| LatticeECP3 PCS in Gigabit Ethernet and SGMII Modes             | 8-42 |

| XAUI Mode                                                       |      |

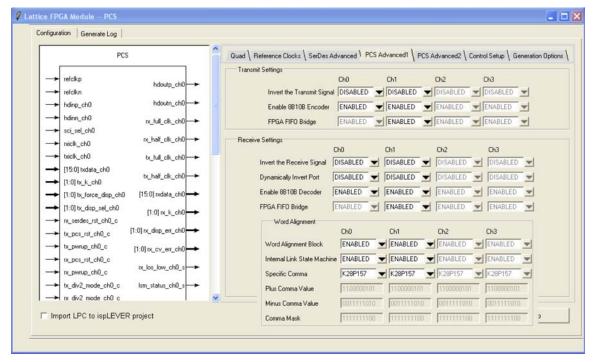

| LatticeECP3 PCS in PCI Express Revision 1.1 (2.5Gpbs) Mode      |      |

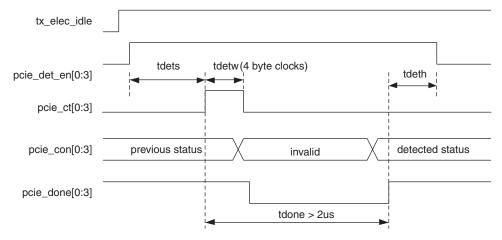

| PCI Express Beacon Support                                      |      |

| SDI (SMPTE) Mode                                                |      |

| Serial RapidIO (SRIO) Mode                                      |      |

| Serial Digital Video and Out-Of-Band Low Speed SERDES Operation |      |

| Open Base Station Architecture Initiative (OBSAI)               |      |

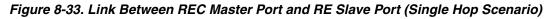

| Common Public Radio Interface (CPRI)                            |      |

| SONET/SDH                                                       | 8-55 |

| FPGA Interface Clocks                                       |            |

|-------------------------------------------------------------|------------|

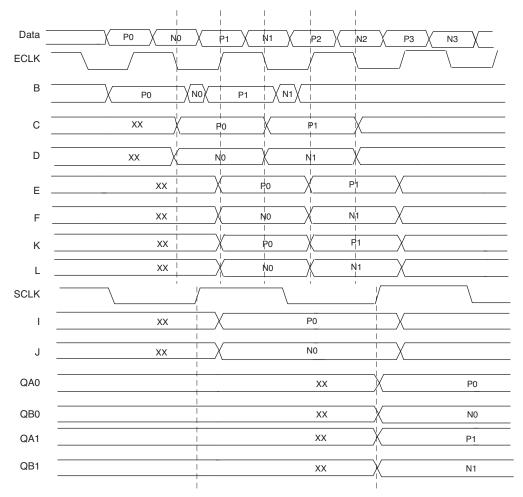

| Case I_a: 8/10-Bit, CTC FIFO and RX/TX FIFOs Not Bypassed   | 8-59       |

| Case I_b: 8/10-Bit, CTC FIFO Bypassed                       |            |

| Case I_c: 8/10-Bit, RX/TX FIFO Bypassed                     |            |

| Case I_d: 8/10-Bit, CTC FIFO and RX/TX FIFOs Bypassed       |            |

| Case II_a: 16/20-bit, CTC FIFO and RX/TX FIFOs NOT Bypassed |            |

| Case II_b: 16/20-bit, CTC FIFO Bypassed                     |            |

| SERDES/PCS Block Latency                                    |            |

| SERDES Client Interface                                     |            |

| Interrupts and Status                                       | 8-68       |

| SERDES Debug Capabilities                                   | 8-69       |

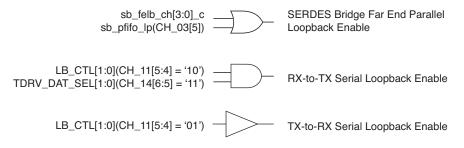

| PCS Loopback Modes                                          | 8-69       |

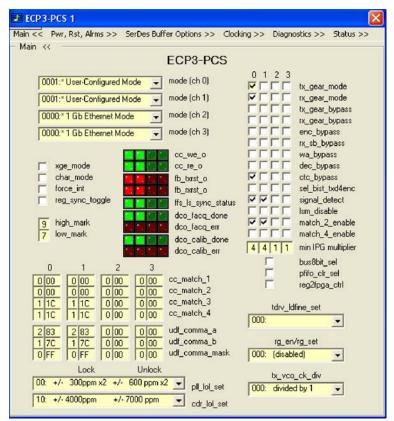

| ORCAstra                                                    |            |

| Other Design Considerations                                 |            |

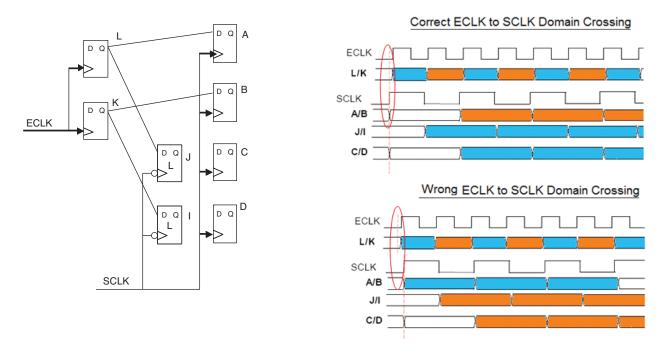

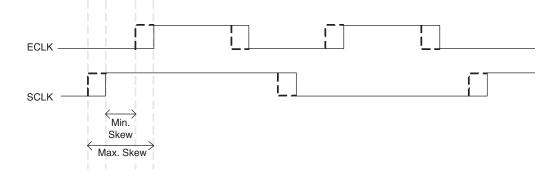

| 16/20-Bit Word Alignment                                    |            |

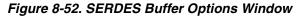

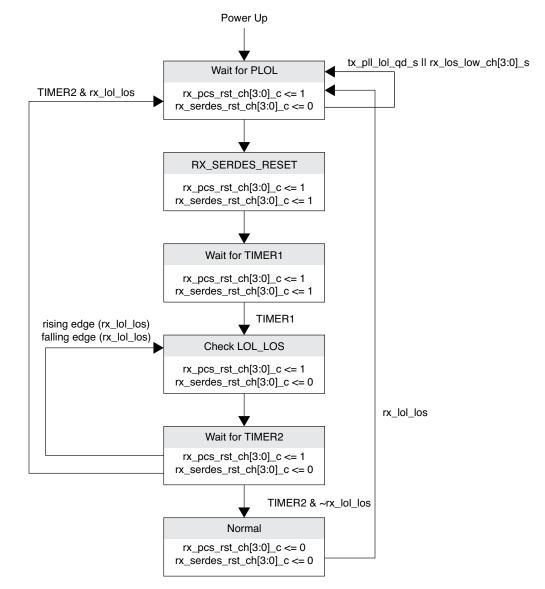

| SERDES/PCS RESET                                            | 8-79       |

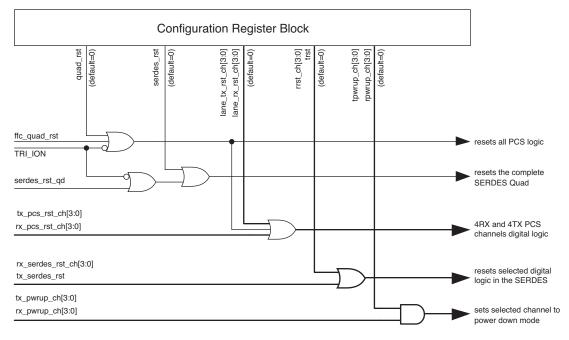

| Reset Sequence and Reset State Diagram                      | 8-79       |

| Reset Sequence Generation                                   | 8-79       |

| Lock Status Signals Definitions                             | 8-79       |

| TX Reset Sequence                                           | 8-79       |

| RX Reset Sequence                                           | 8-79       |

| References                                                  |            |

| Technical Support Assistance                                |            |

| Revision History                                            |            |

| Appendix A. Configuration Registers                         | 8-85       |

| Quad Registers Overview                                     |            |

| Per Quad PCS Control Registers Details                      | 8-85       |

| Per Quad PCS Control Registers Details                      |            |

| Per Quad Reset and Clock Control Registers Details          |            |

| Per Quad PCS Status Registers Details                       |            |

| Per Quad SERDES Status Registers Details                    |            |

| Channel Registers Overview                                  |            |

| Per Channel PCS Control Registers Details                   |            |

| Per Channel SERDES Control Registers Details                |            |

| Per Channel Reset and Clock Control Registers Details       |            |

| Per Channel PCS Status Registers Details                    |            |

| Per Channel SERDES Status Registers Details                 |            |

| Appendix B. Register Settings for Various Standards         |            |

| Per Channel Register Settings for Various Standards         |            |

| Per Quad Register Settings for Various Standards            |            |

| Appendix C. Attribute Cross Reference Table                 |            |

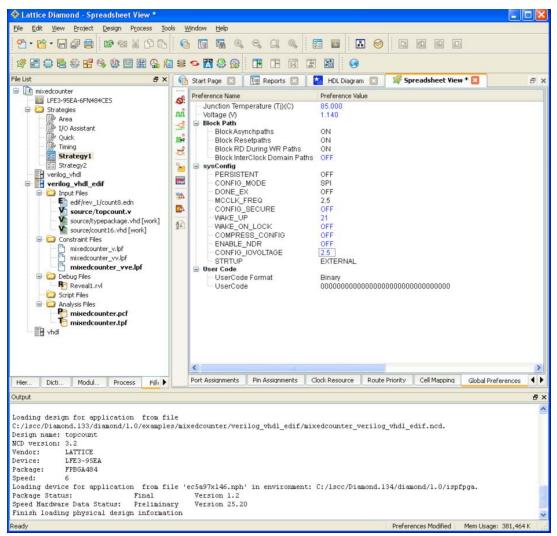

| Appendix D. Lattice Diamond Overview                        |            |

| Converting an ispLEVER Project to Lattice Diamond           |            |

| Importing an ispLEVER Design Project                        |            |

| Adjusting PCS Modules                                       |            |

| Regenerate PCS Modules                                      |            |

| Using IPexpress with Lattice Diamond                        |            |

| Creating a New Simulation Project Using Simulation Wizard   |            |

| LatticeECP3 sysIO Usage Guide                               | <b>.</b> . |

| Introduction                                                |            |

| sysIO Buffer Overview                                       |            |

| Supported sysIO Standards                                   |            |

| sysIO Banking Scheme                                        |            |

| V <sub>CCIO</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)                |            |

|                                                                                | 0.5  |

|--------------------------------------------------------------------------------|------|

| V <sub>CCAUX</sub> (3.3V)                                                      |      |

| V <sub>CCJ</sub> (1.2V/1.5V/1.8V/2.5V/3.3V)                                    |      |

| Input Reference Voltage (V <sub>REF1</sub> , V <sub>REF2</sub> )               |      |

| VREF1 for DDR Memory Interface                                                 |      |

| VTT Termination Voltage                                                        |      |

| Hot Socketing Support                                                          |      |

| Mixed Voltage Support in a Bank                                                |      |

| sysIO Standards Supported Per Bank                                             |      |

| sysIO Buffer Configurations                                                    |      |

| Bus Maintenance Circuit                                                        |      |

| Programmable Drive                                                             |      |

| Programmable Slew Rate                                                         |      |

| Open Drain Control                                                             |      |

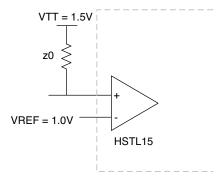

| Differential SSTL and HSTL Support                                             |      |

|                                                                                |      |

| PCI Support with Programmable PCICLAMP                                         |      |

| Differential I/O Support                                                       |      |

| Differential SSTL and HSTL                                                     |      |

| Differential LVCMOS33                                                          |      |

| GTL+ Input Support                                                             | 9-9  |

| On-Chip Termination                                                            |      |

| Equalization Setting                                                           |      |

| Software sysIO Attributes                                                      |      |

|                                                                                |      |

| OPENDRAIN                                                                      |      |

| DRIVE                                                                          |      |

| DIFFDRIVE                                                                      |      |

| MULTDRIVE                                                                      |      |

|                                                                                |      |

|                                                                                |      |

| DIFFRESISTOR                                                                   |      |

| EQ_CAL                                                                         |      |

| PULLMODE                                                                       |      |

| PCICLAMP                                                                       |      |

| SLEWRATE                                                                       |      |

| INBUF                                                                          |      |

| FIXEDDELAY                                                                     |      |

| DIN/DOUT                                                                       |      |

| LOC                                                                            |      |

| Design Considerations and Usage                                                |      |

| Banking Rules                                                                  |      |

| Differential I/O Rules                                                         |      |

|                                                                                |      |

| Technical Support Assistance                                                   |      |

| Revision History                                                               |      |

| Appendix A. HDL Attributes                                                     |      |

| VHDL Synplify Pro                                                              |      |

| Verilog Synplicity                                                             |      |

| Appendix B. sysIO Attributes Using the ispLEVER Design Planner User Interface  |      |

| Appendix C. sysIO Attributes Using the Diamond Spreadsheet View User Interface |      |

| LatticeECP3 sysCLOCK PLL/DLL Design and Usage Guide                            |      |

| Introduction                                                                   |      |

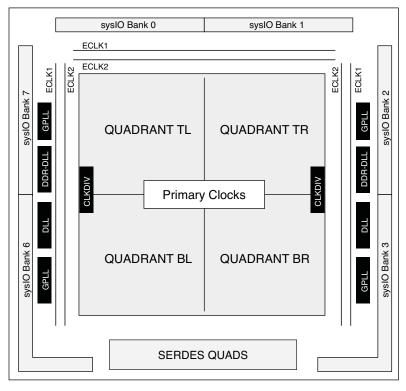

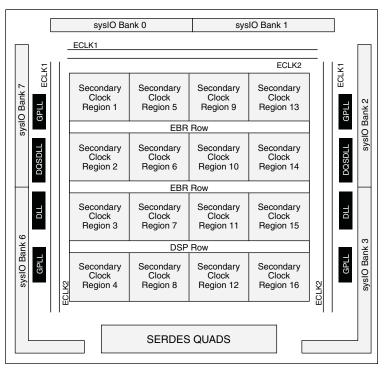

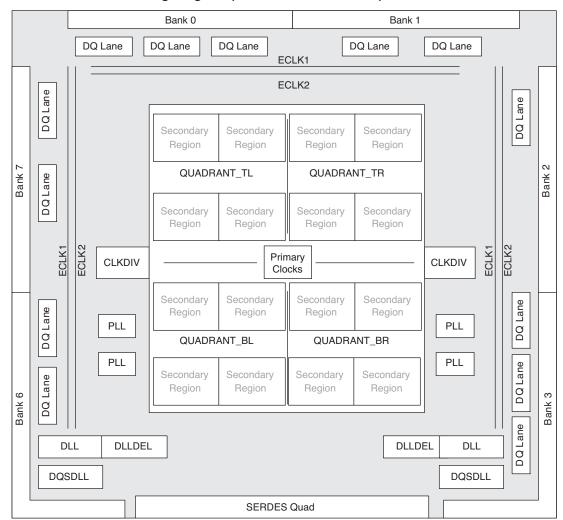

| Clock/Control Distribution Network                                             | 10-1 |

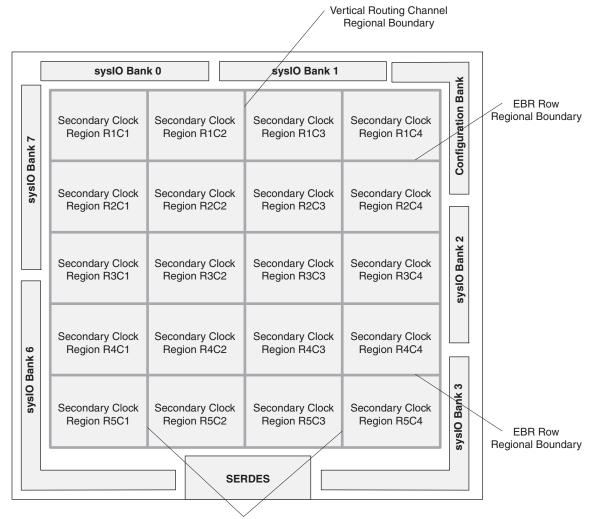

| LatticeECP3 Top-Level View                                                     |      |

| Primary Clocks                                                                 |      |

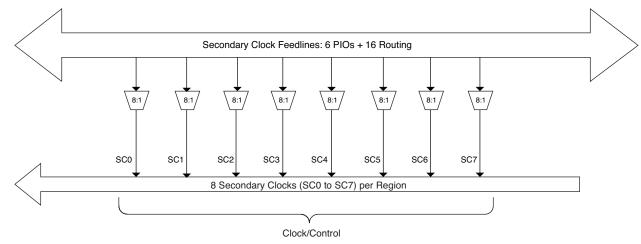

| Secondary Clocks                                                               |      |

| Edge Clocks                                                                    |      |

|                                                                                |      |

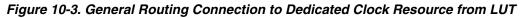

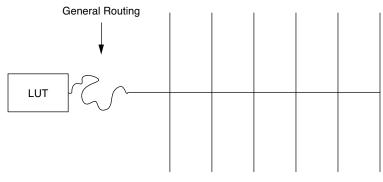

| General Routing for Clocks                             | 10-4  |

|--------------------------------------------------------|-------|

| Additional Connectivity for Dedicated Clock Resources  |       |

| Very Small Clock Domains                               |       |

| Static Timing Analysis of General Routing Clocks       |       |

| Specifying Clocks in the Design Tools                  |       |

| Global Primary Clock and Quadrant Primary Clock        |       |

| Global Primary Clock                                   |       |

| Primary-Pure and Primary-DCS.                          |       |

| Quadrant Primary Clock                                 |       |

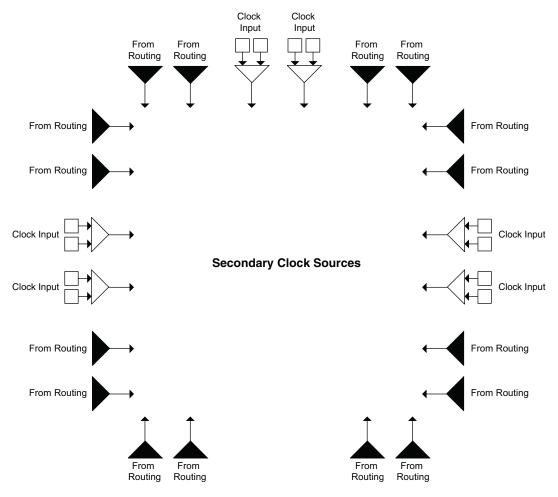

| Global Secondary Clock and Regional Secondary Clocks   |       |

| Global Secondary Clocks                                |       |

| Regional Secondary Clocks                              |       |

| Secondary Region Clock Preferencing                    |       |

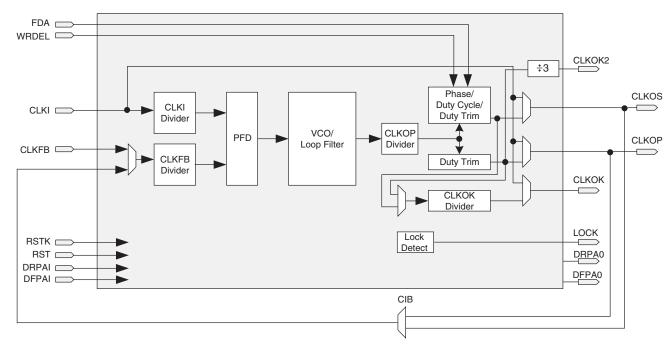

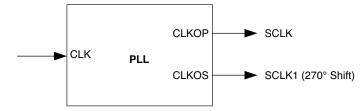

| sysCLOCK™ PLL                                          |       |

|                                                        |       |

| Functional Description                                 |       |

| PLL Divider and Delay Blocks                           |       |

| PLL Inputs and Outputs                                 |       |

| CLKI Input                                             |       |

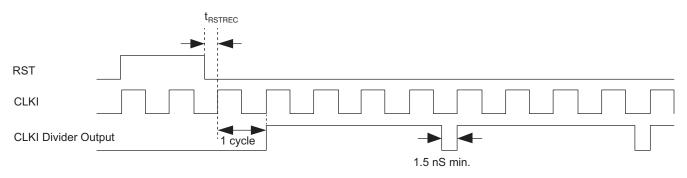

| RST Input                                              |       |

| RSTK Input                                             |       |

| CLKFB Input                                            |       |

| CLKOP Output                                           |       |

| CLKOS Output with Phase and Duty Cycle Select          |       |

| CLKOK Output with Lower Frequency                      | 10-11 |

| CLKOK2 Output                                          | 10-11 |

| LOCK Output                                            | 10-12 |

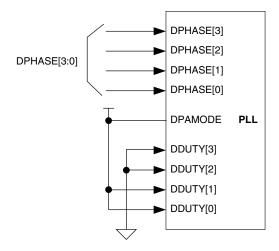

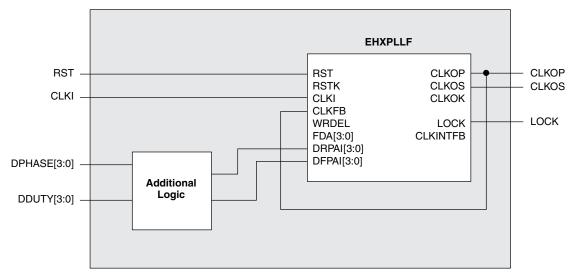

| Dynamic Phase and Dynamic Duty Cycle Adjustment        | 10-12 |

| Dynamic Phase Adjustment/Duty Cycle Select             | 10-12 |

| Fine Delay Ports                                       |       |

| LatticeECP3 PLL Modules                                | 10-13 |

| LatticeECP3 PLL Library Definition                     |       |

| EPLLD Design Migration from LatticeECP2 to LatticeECP3 |       |

| Dynamic Phase/Duty Mode                                |       |

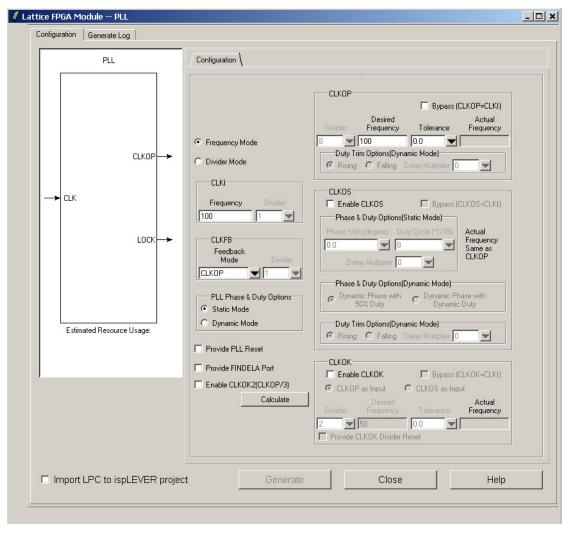

| PLL Usage in IPexpress.                                |       |

| Configuration Tab                                      |       |

| PLL Modes of Operation                                 |       |

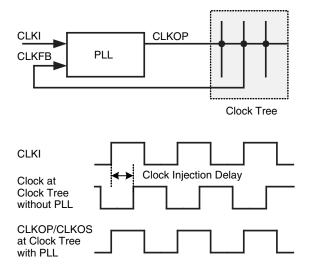

| PLL Clock Injection Removal                            |       |

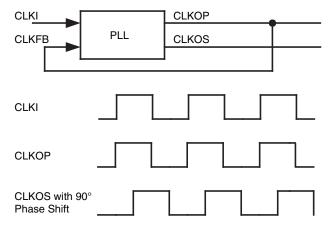

| PLL Clock Phase Adjustment                             | 10-19 |

| IPexpress Output                                       |       |

| Notes on PLL Usage                                     |       |

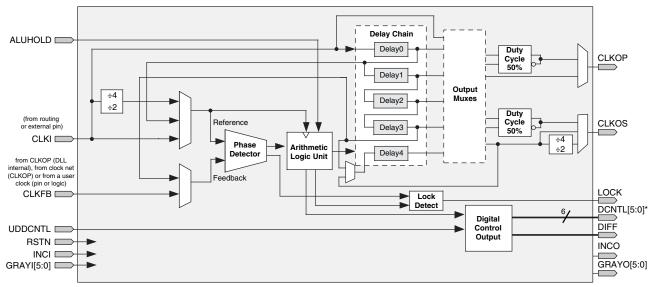

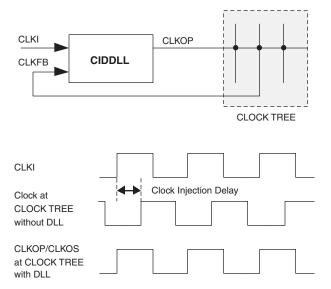

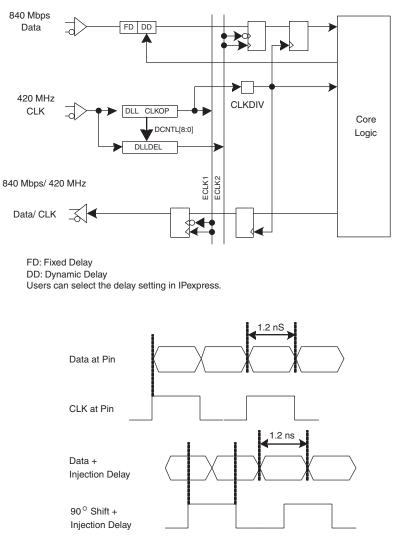

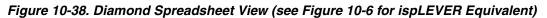

| sysCLOCK DLL                                           |       |

| DLL Overview                                           |       |

| DLL Inputs and Outputs                                 |       |

| DLL Attributes                                         |       |

| DLL Attributes                                         |       |

| •                                                      |       |

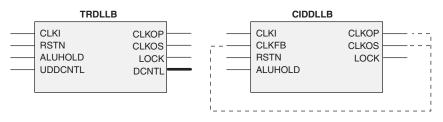

| DLL Library Element I/Os.                              |       |

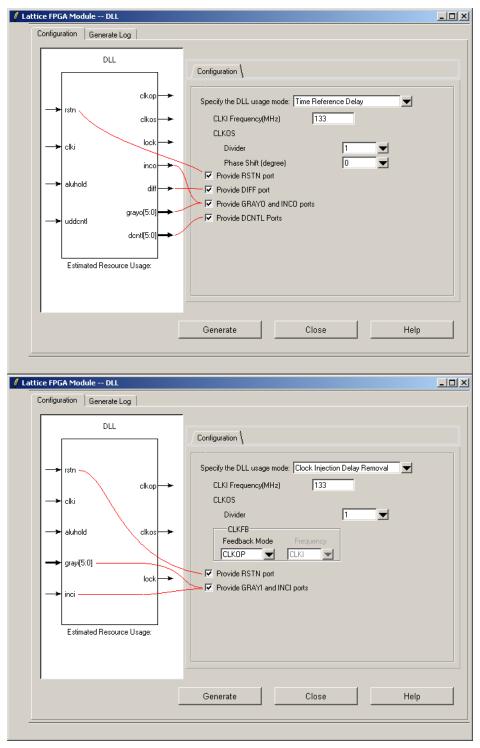

| DLL Modes of Operation                                 |       |

| DLL Usage in IPexpress                                 |       |

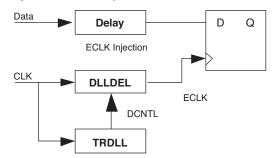

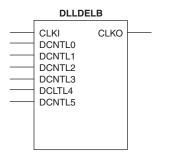

| DLLDEL (Slave Delay Line)                              |       |

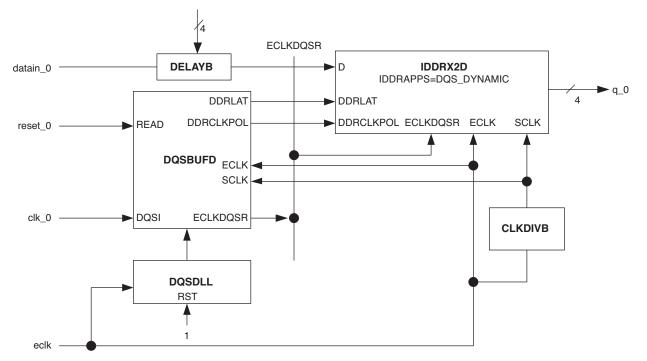

| DQSDLL and DQSDEL                                      |       |

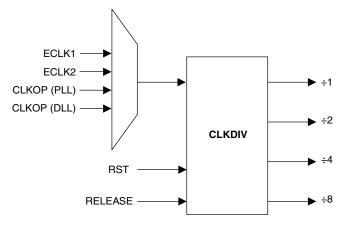

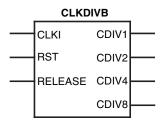

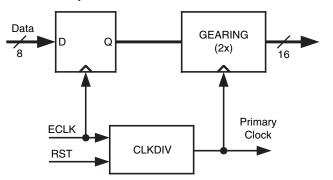

| Clock Dividers (CLKDIV)                                |       |

| CLKDIV Library Definition                              |       |

| CLKDIV Declaration in VHDL Source Code                 | 10-30 |

| CLKDIV Usage with Verilog - Example                    |       |

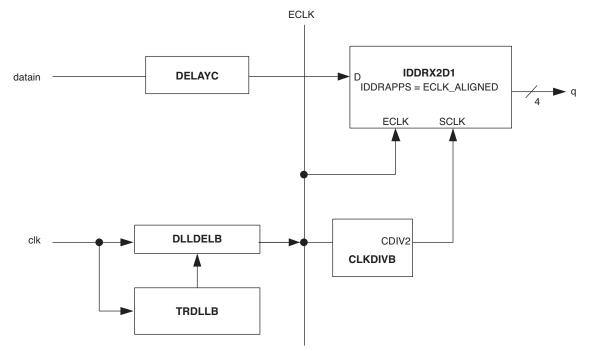

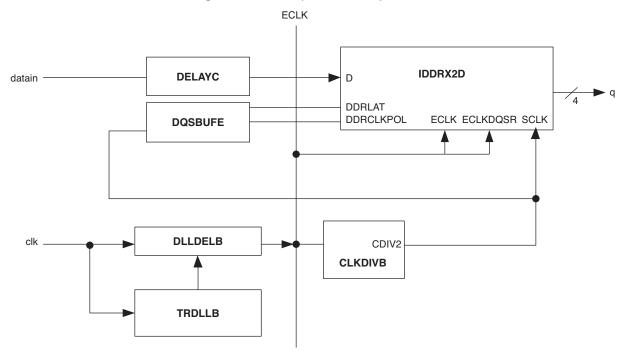

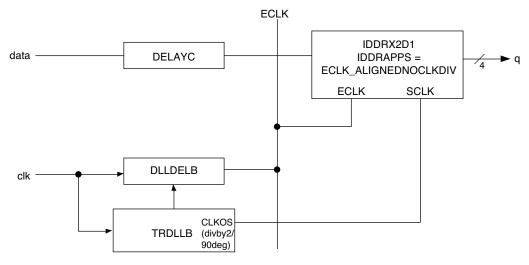

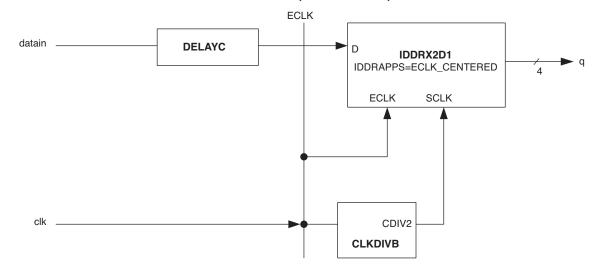

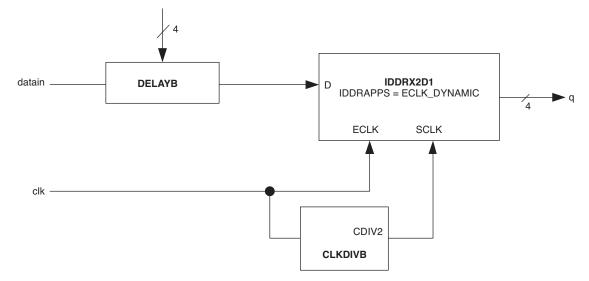

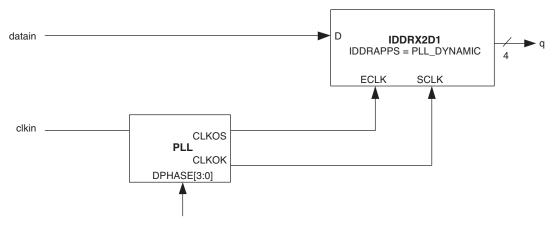

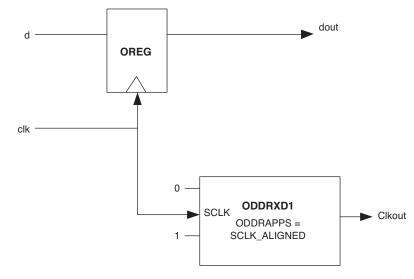

| CLKDIV Example Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

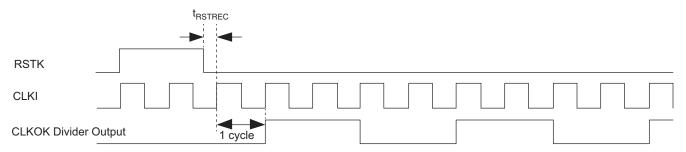

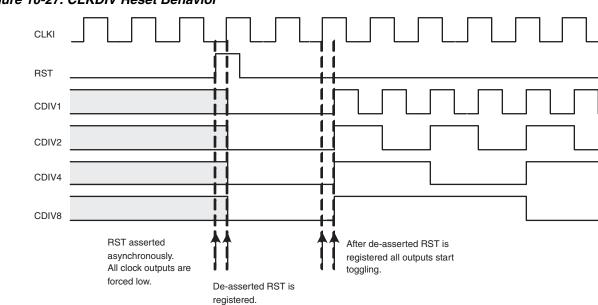

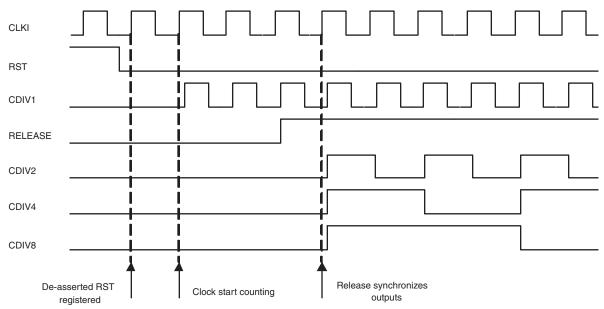

| Reset Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Release Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

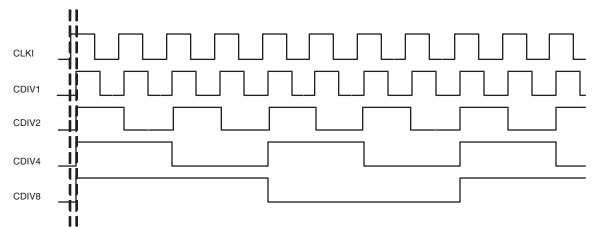

| CLKDIV Inputs-to-Outputs Delay Matching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

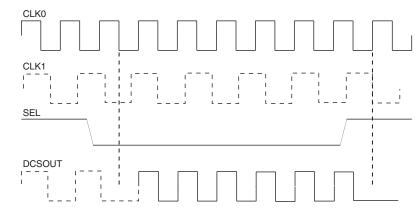

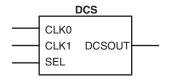

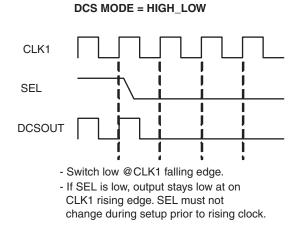

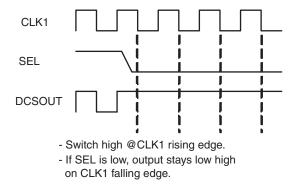

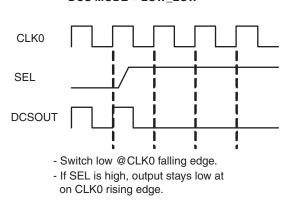

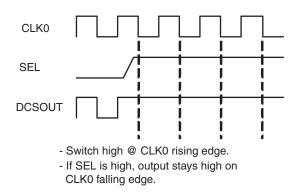

| DCS (Dynamic Clock Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DCS Library Definition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

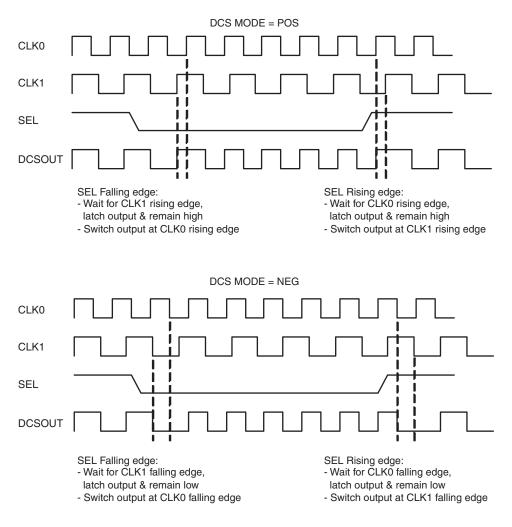

| DCS Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DCS Usage with VHDL - Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DCS Usage with Verilog - Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Oscillator (OSCF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OSC Library Symbol (OSCF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OSC Usage with VHDL - Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OSC Usage with Verilog - Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Setting Clock Preferences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |