# PIC16C432

# PIC16C432 Data Sheet Errata

The PIC16C432 parts you have received conform functionally to the Device Data Sheet (DS41140**A**), except for the anomalies described below.

None.

bit bit

bit bit

# Clarifications/Corrections to the Data Sheet:

In the Device Data Sheet (DS41140**A**), the following clarifications and corrections should be noted.

The positions of LINTX and LINVDD are shown in Register 1.

#### REGISTER 1: LININTF REGISTER (ADDRESS 90h)

- n = Value at POR

| U-0                                        | U-0            | U-0        | U-0           | U-0           | R/W-1       | U-0           | R/W-1 |  |

|--------------------------------------------|----------------|------------|---------------|---------------|-------------|---------------|-------|--|

|                                            |                |            |               |               | LINTX       |               | LINVD |  |

| bit 7                                      | •              |            | •             |               |             |               | bit   |  |

| Unimplem                                   | ented: Read    | d as '0'   |               |               |             |               |       |  |

| LINTX: LIN                                 | Bus Transr     | nit bit    |               |               |             |               |       |  |

| 1 = LIN Bu                                 | s line is high | ı          |               |               |             |               |       |  |

| 0 = LIN Bu                                 | s line is low  |            |               |               |             |               |       |  |

| Unimplem                                   | ented: Read    | d as '0'   |               |               |             |               |       |  |

| LINVDD: LIN Bus Transceiver VDD Supply bit |                |            |               |               |             |               |       |  |

| 1 = VDD is                                 | supplied to t  | he LIN Bus | s transceiver | via microcor  | ntroller    |               |       |  |

| 0 = VDD is                                 | not supplied   | to the LIN | Bus transce   | iver          |             |               |       |  |

| Note:                                      | Transceiver    | VDD is sam | e as microc   | ontroller VDD |             |               |       |  |

|                                            |                |            |               |               |             |               |       |  |

| Legend:                                    |                |            |               |               |             |               |       |  |

| R = Reada                                  | ble bit        | W = V      | Vritable bit  | U = Unim      | plemented b | it, read as ' | 0'    |  |

'0' = Bit is cleared

'1' = Bit is set

x = Bit is unknown

The description of the BACT (Bus activity output) function in Table 3-1 has changed. Refer to updated Table 3-1:

#### TABLE 3-1: PIC16C432 PINOUT DESCRIPTION

| Name         | DIP/<br>SSOP<br>Pin #               | l/O/P<br>Type | Buffer<br>Type                            | Description                                                                                                                                                                                                       |  |  |  |

|--------------|-------------------------------------|---------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| OSC1/CLKIN   | 17                                  | 1             | ST/CMOS                                   | Oscillator crystal input/external clock source input.                                                                                                                                                             |  |  |  |

| OSC2/CLKOUT  | 16                                  | 0             | _                                         | Oscillator crystal output. Connects to crystal or resonator in<br>Crystal Oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |  |  |  |

| MCLR/Vpp     | 5                                   | I/P           | ST                                        | Master Clear (Reset) input/programming voltage input. Th pin is an active low RESET to the device.                                                                                                                |  |  |  |

|              |                                     |               |                                           | PORTA is a bi-directional I/O port.                                                                                                                                                                               |  |  |  |

| RA0/AN0      | 18                                  | I/O           | ST                                        | Analog comparator input.                                                                                                                                                                                          |  |  |  |

| BACT         | 19                                  | 0             | _                                         | Bus activity output. No connection if not used. It is a CMOS levels representation of the LIN pin                                                                                                                 |  |  |  |

| RA2/AN2/VREF | 2                                   | I/O           | ST                                        | Analog comparator input or VREF output.                                                                                                                                                                           |  |  |  |

| RA3/AN3      | 3                                   | I/O           | ST                                        | Analog comparator input/output.                                                                                                                                                                                   |  |  |  |

| RA4/T0CKI    | 4                                   | I/O           | ST                                        | Can be selected to be the clock input to the Timer0 timer/<br>counter or a comparator output. Output is open drain type.                                                                                          |  |  |  |

|              |                                     |               |                                           | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                     |  |  |  |

| RB0/INT      | 7                                   | I/O           | TTL/ST <sup>(1)</sup>                     | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                                        |  |  |  |

| RB1          | 8                                   | I/O           | TTL                                       |                                                                                                                                                                                                                   |  |  |  |

| RB2          | 9                                   | I/O           | TTL                                       |                                                                                                                                                                                                                   |  |  |  |

| RB3          | 10                                  | I/O           | TTL                                       |                                                                                                                                                                                                                   |  |  |  |

| RB4          | 11                                  | I/O           | TTL                                       | Interrupt-on-change pin.                                                                                                                                                                                          |  |  |  |

| RB5          | 12                                  | I/O           | TTL                                       | Interrupt-on-change pin.                                                                                                                                                                                          |  |  |  |

| RB6          | 13                                  | I/O           | TTL/ST <sup>(2)</sup>                     | Interrupt-on-change pin. Serial programming clock.                                                                                                                                                                |  |  |  |

| RB7          | 14                                  | I/O           | TTL/ST <sup>(2)</sup>                     | Interrupt-on-change pin. Serial programming data.                                                                                                                                                                 |  |  |  |

| LIN          | 1                                   | I/O           | HV/OD                                     | High Voltage Bi-directional Bus Interface.                                                                                                                                                                        |  |  |  |

| VBAT         | 20                                  | Р             | —                                         | Battery Input Voltage.                                                                                                                                                                                            |  |  |  |

| Vss          | 6, 19                               | Р             | —                                         | Ground reference for logic and I/O pins.                                                                                                                                                                          |  |  |  |

| Vdd          | 15                                  | Р             | —                                         | Positive supply for logic and I/O pins.                                                                                                                                                                           |  |  |  |

| Legend:      | O = Outp<br>— = Not u<br>TTL= TTL i | ised          | I/O = Input/C<br>I = Input<br>OD = Open I | ST = Schmitt Trigger input                                                                                                                                                                                        |  |  |  |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

Page 27 of the Data Sheet, Section 6.2 LIN Bus Interfacing, Section 6.3 LIN Bus Hardware Interface and Section 6.5 Wake-up from SLEEP upon Bus Activity, have been changed to the following:

#### 6.2 LIN Bus Interfacing

The LIN protocol is implemented and programmed by the user, using the LINTX and LINRX bits, which are used to interface to the transceiver. The LIN Bus firmware transmits by toggling the LINTX bit in the LININTF register and is read by reading the LINRX bit in the PORTA register. All aspects of the protocol are handled by software (i.e. bit-banged), where the transceiver is used as the physical interface to the LIN Bus network.

For an interrupt based LIN Bus slave implementation, please refer to AN729, available on Microchip's website (www.microchip.com). This application note is based on PIC16C622, but can be converted for either PIC16C432 or PIC16C433.

For the PIC16C432, the changes required include but are not limited to:

- 1. Change the include file to "p16C432.inc".

- Use LINTX bit in LININTF register instead of TXLINEPIN in PORTB to transmit. Note LIN-INTF is in bank 1.

- 3. Use LINRX bit in PORTA register instead of TXLINEPIN in PORTB to receive.

- 4. Connect the bus to LIN pin to receive and transmit instead of PORTB<0> and PORTB<4>.

- 5. Ensure that LINRX and LINVDD remain set.

| Note: | The LINTX is bit 2 of the LININTF register |

|-------|--------------------------------------------|

|       | and not bit 1 as documented in the         |

|       | PIC16C432 data sheet.                      |

If the LINTX bit is left cleared, no other nodes on the network will be able to communicate on the LIN Bus for this is the dominate state for the protocol. The transceiver can be powered down by clearing the LINVDD bit in the LININTF register. This can be useful to reduce current consumption but does not allow the microcontroller to wake-up on LIN Bus activity because the transceiver will be disabled. It is recommended that the firmware verify each bit transmitted, by comparing the LINTX and LINRX bits, to ensure no bus contention or hardware failure has occurred. The LINTX bit has no associated TRIS bit and is always an output. The LINRX bit has an associated TRIS bit, TLINRX, in the TRISA register.

Note: TLINRX, bit 1 of TRISA register, must be set to '1' at all times.

#### 6.3 LIN Bus Hardware Interface

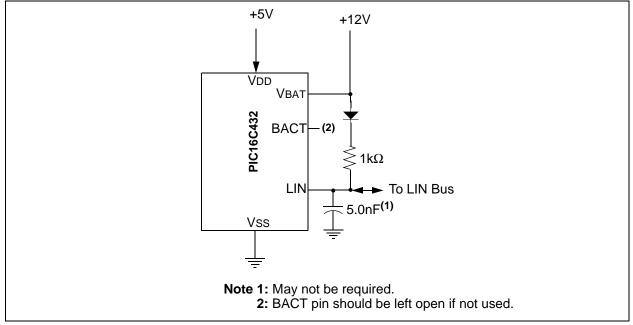

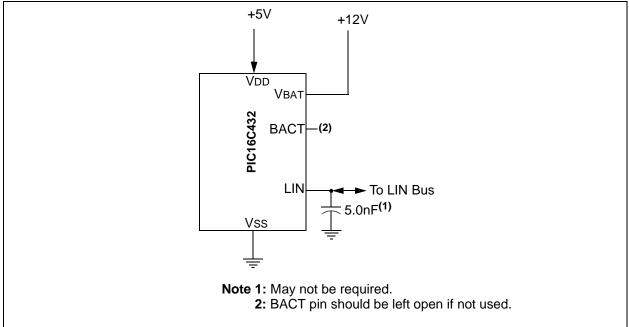

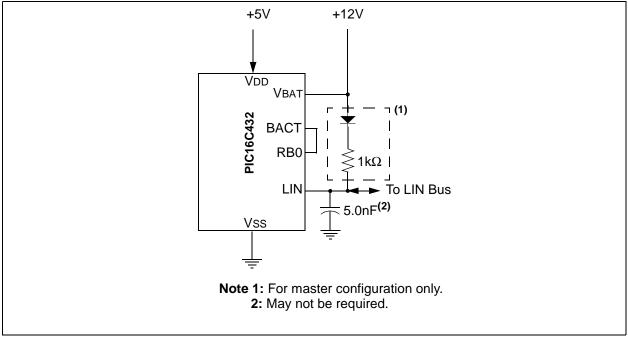

Figure 6-1 shows how to implement a hardware LIN Bus interface in a master configuration and Figure 6-2 in a slave configuration using the PIC16C432. Figure 6-3 shows how to implement the hardware for a master configuration using BACT pin to generate a wake-up interrupt using RB0. The transceiver has an internal series resistor and diode, as defined in the LIN 1.2 specification, connecting VBAT and LIN.

**Note:** No resistor is required between VBAT pin and 12V supply and for slave configuration, no resistor is required between VBAT and LIN.

#### 6.5 Wake-up from SLEEP upon Bus Activity

The PIC16C432 can wake-up from SLEEP upon bus activity in two ways:

- 1. With the use of the comparators.

- 2. Connecting BACT to one of PORTB<0,4:7> pins.

In case the comparators are used to wake-up the device upon bus activity, a reference to the LIN Bus signal has to be supplied. This is usually VDD/2. The reference can either be an external reference or the internal voltage reference. Once the device is in SLEEP mode, the comparator interrupt will wake-up the device. On RESET, LINRX is configured as an analog comparator input (Section 8.1 of Data Sheet) which can be used to generate an interrupt to wake-up the device from SLEEP on bus activity. The LINRX bit will not receive data from the bus configured as an analog input, therefore, after wake-up from comparator interrupt or RESET, LINRX must be configured as a digital input to read the bus.

The BACT output is a CMOS-levels representation of the LIN pin. This signal can be routed to one of the PORTB<0,4:7> pins. The RB0/INT external interrupt or PORTB<4:7> interrupt-on-change wakes up the device from SLEEP. Any one of the five PORTB pins can be used for wake-up where PORTB<0> offers multiple configuration options (Section 10.5.1 of Data Sheet) and PORTB<4:7> are interrupt-on-change (Section 10.5.3 of Data Sheet).

Note: BACT pin is an output and must be left open if unused.

#### FIGURE 6-1: TYPICAL LIN BUS MASTER APPLICATION

A new figure has been added to show LIN Bus slave configuration, Figure 6-2:

#### FIGURE 6-2: TYPICAL LIN BUS SLAVE APPLICATION

A new figure has been added to show LIN Bus configuration using Wake-up interrupt, Figure 6-3:

#### FIGURE 6-3: LIN BUS APPLICATION USING WAKE-UP INTERRUPT

#### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH LIN TRANSCEIVER

| Address | Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1                 | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>RESETS |

|---------|---------|-------|-------|-------|--------|--------|--------|-----------------------|--------|------------------|---------------------------------|

| 05h     | PORTA   | -     | _     |       | RA4    | RA3    | RA2    | LINRX                 | RA0    | x 0000           | u 0000                          |

| 85h     | TRISA   |       | _     | _     | TRISA4 | TRISA3 | TRISA2 | TLINRX <sup>(2)</sup> | TRISA0 | 1 1111           | 1 1111                          |

| 90h     | LININTF |       |       | _     |        |        | LINTX  | _                     | LINVDD | 1-1              | 1-1                             |

Legend: x = unknown, u = unchanged, - = Unimplemented locations read as '0'.

Note 1: Shaded bits are not used by LIN transceiver

2: TLINRX must be set to '1' at all times.

The Electrical Specifications have been changed to include the maximum current sunk by LIN and BACT pins, as shown in the following table in Section 13.0 of the PIC16C432 Data Sheet.

## **13.0 Electrical Specifications for PIC16C432**

#### Absolute Maximum Ratings (†)

| Ambient Temperature under bias                                                                                                                  |                   |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| Storage Temperature                                                                                                                             | 65° to +150°C     |  |  |  |  |

| Voltage on any pin with respect to Vss (except VDD and $\overline{\text{MCLR}}$ )                                                               | 0.6V to VDD +0.6V |  |  |  |  |

| Voltage on VDD with respect to Vss                                                                                                              | 0 to +7.0V        |  |  |  |  |

| Voltage on RA4 with respect to Vss                                                                                                              | 8.5V              |  |  |  |  |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                    | 0 to +14V         |  |  |  |  |

| Voltage on RA4 with respect to Vss                                                                                                              | 8.5V              |  |  |  |  |

| Total power Dissipation (Note 1)                                                                                                                | 1.0W              |  |  |  |  |

| Maximum Current out of Vss pin                                                                                                                  | 300 mA            |  |  |  |  |

| Maximum Current into VDD pin                                                                                                                    | 250 mA            |  |  |  |  |

| Input Clamp Current, Iк (VI <0 or VI> VDD)                                                                                                      | ±20 mA            |  |  |  |  |

| Output Clamp Current, IOK (VO <0 or VO>VDD)                                                                                                     | ±20 mA            |  |  |  |  |

| Maximum Output Current sunk by any I/O pin                                                                                                      | 25 mA             |  |  |  |  |

| Maximum Output Current sourced by any I/O pin                                                                                                   | 25 mA             |  |  |  |  |

| Maximum Current sunk by PORTA and PORTB                                                                                                         | 200 mA            |  |  |  |  |

| Maximum Current sourced by PORTA and PORTB                                                                                                      | 200 mA            |  |  |  |  |

| Maximum Current sunk by LIN                                                                                                                     | 200 mA            |  |  |  |  |

| Maximum Current sunk by BACT                                                                                                                    | 1.8 mA            |  |  |  |  |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pois = Vio x {IOH} + $\Sigma$ {(VOH} + $\Sigma$ {(VOH) x IOH} + $\Sigma$ (VOH x IOH) |                   |  |  |  |  |

**Note 1:** Power dissipation is calculated as follows: PDIS = VDD x {IDD -  $\Sigma$  IOH} +  $\Sigma$  {(VDD-VOH) x IOH} +  $\Sigma$ (VOI x IOL)

**2:** Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin, rather than pulling this pin directly to Vss.

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## APPENDIX A: REVISION HISTORY

<u>Rev. A Document (4/2001)</u> First revision of this document.

Rev. B Document (9/2001)

Under Clarifications/Corrections to the Data Sheet, corrections have been made to the following:

TABLE 3-1 - description of the BACT function.

Page 27:

Section 6.2 - LIN Bus Interfacing.

FIGURE 6-2 - added to show connections using Wakeup interrup.

Section 6.3 - LIN Bus Hardware Interface.

Section 6.5 - Wake-up from SLEEP upon Bus Activity.

13.0 Electrical Specifications for PIC16C432 - changed to include the maximum current sunk by LIN and BACT pins.

Rev. C Document (10/2001)

Change title of document from Rev. B Silicon Errata to Data Sheet Errata. Deleted 'Rev. C' from first paragraph, page 1.

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microID, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Tum Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2001, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEEL00® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

Rocky Mountain 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

Boston 2 Lan Drive, Suite 120 Westford, MA 01886

Tel: 978-692-3848 Fax: 978-692-3821 Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas 4570 Westgrove Drive, Suite 160

Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924 **Dayton**

Two Prestige Place, Suite 130 Miamisburg, OH 45342 Tel: 937-291-1654 Fax: 937-291-9175

Detroit Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334

Tel: 248-538-2250 Fax: 248-538-2260 **Kokomo**

2767 S. Albright Road Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387 **Los Angeles**

18201 Von Karman, Suite 1090 Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338 New York

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

San Jose Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915 Bei Hai Wan Tai Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104 China - Chengdu Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China

Tel: 86-28-6766200 Fax: 86-28-6766599 China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Rm. 531, North Building Fujian Foreign Trade Center Hotel 73 Wusi Road Fuzhou 350001, China Tel: 86-591-7557563 Fax: 86-591-7557572 **China - Shanghai** Microchip Technology Consulting (Shanghai)

Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tol: 96.21, 6075, 5700, Fax: 96.21, 61

Tel: 86-21-6275-5700 Fax: 86-21-6275-5060 China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086 **Hong Kong** Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 **India** Microchip Technology Inc.

India Liaison Office Divyasree Chambers 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

#### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471-6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

EUROPE

Denmark Microchip Technology Nordic ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Microchip Technology GmbH Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883 United Kingdom Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

10/01/01