# **Atmel ATMEGA256RFR2 Xplained Pro**

## **Preface**

The Atmel® ATMEGA256RFR2 Xplained Pro evaluation kit is hardware platform to evaluate the ATmega256RFR2 microcontroller.

Supported by the Atmel Studio integrated development platform, the kit provides easy access to the features of the Atmel ATmega256RFR2 and explains how to integrate the device in a customer design.

The Xplained Pro MCU series evaluation kits include an on-board Embedded Debugger, and no external tools are necessary to program or debug the ATmega256RFR2.

The Xplained Pro extension series evaluation kits offers additional peripherals to extend the features of the board and ease the development of customer designs.

# **Table of Contents**

| Pre | eface                                |                                                                                                                                                                                                                                                                            | 1                                                 |

|-----|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1.  | 1.1.<br>1.2.                         | duction  Features  Kit overview                                                                                                                                                                                                                                            | 3                                                 |

| 2.  | Getti<br>2.1.<br>2.2.<br>2.3.        | Quick-start Connecting the kit Design documentation and related links                                                                                                                                                                                                      | 5<br>5                                            |

| 3.  | Xpla<br>3.1.<br>3.2.<br>3.3.<br>3.4. | ined Pro  Embedded Debugger  Hardware identification system  Power supply  3.3.1. Measuring ATmega256RFR2 power consumption  Standard headers and connectors  3.4.1. Xplained Pro standard extension header  3.4.2. Power header                                           | 6<br>7<br>7<br>7<br>7                             |

| 4.  | Hard<br>4.1.<br>4.2.                 | Connectors 4.1.1. I/O extension headers 4.1.2. Other headers Peripherals 4.2.1. Crystals 4.2.2. Mechanical buttons 4.2.3. LED 4.2.4. RF 4.2.5. Temperature sensor Embedded Debugger implementation 4.3.1. JTAG 4.3.2. Virtual COM port 4.3.3. Atmel Data Gateway Interface | 9<br>12<br>13<br>13<br>13<br>14<br>14<br>14<br>15 |

| 5.  | Hard<br>5.1.<br>5.2.                 | Iware revision history and known issues                                                                                                                                                                                                                                    | 16                                                |

| 6.  | Docu                                 | ument revision history                                                                                                                                                                                                                                                     | 17                                                |

| 7.  |                                      | uation board/kit important notice                                                                                                                                                                                                                                          |                                                   |

## 1. Introduction

## 1.1 Features

- Atmel® ATmega256RFR2 microcontroller

- Embedded Debugger (EDBG)

- USB interface

- Programming and debugging (target) through JTAG

- Virtual COM-port interface to target via UART

- Atmel Data Gateway Interface (DGI) to target via SPI or TWI

- Four GPIOs connected to target for code instrumentation

- Digital I/O

- Two mechanical buttons (user and reset button)

- One user LED

- Five extension headers

- Antenna

- One ceramic chip antenna (2450BM15A0015E)

- One SMA connector for external antenna

- Temperature sensor and EEPROM (AT30TSE758)

- Two possible power sources

- External power

- Embedded debugger USB

- 16MHz crystal

- 32kHz crystal

#### 1.2 Kit overview

The Atmel ATMEGA256RFR2 Xplained Pro evaluation kit is a hardware platform to evaluate the Atmel ATmega256RFR2.

The kit offers a set of features that enables the ATmega256RFR2 user to get started using the ATmega256RFR2 peripherals right away and to get an understanding of how to integrate the device in their own design.

**EXT3 HEADER**

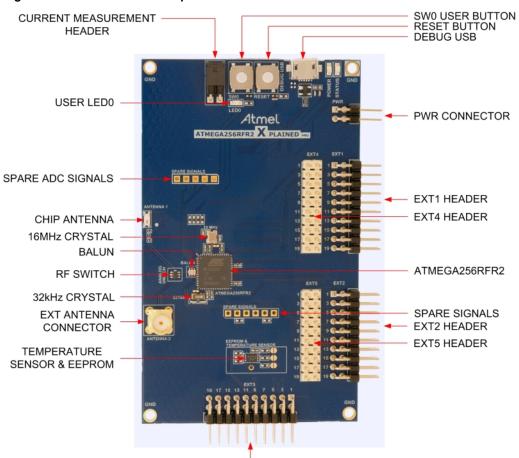

Figure 1.1. ATMEGA256RFR2 Xplained Pro evaluation kit overview.

# 2. Getting started

## 2.1 Quick-start

3 Steps to start exploring the Atmel Xplained Pro Platform

- Download and install Atmel Studio<sup>1</sup>.

- · Launch Atmel Studio.

- Connect an USB cable to the DEBUG USB port.

## 2.2 Connecting the kit

When connecting Atmel ATMEGA256RFR2 Xplained Pro to your computer for the first time, the operating system will do a driver software installation. The driver file supports both 32-bit and 64-bit versions of Microsoft® Windows® XP and Windows 7.

Once connected the green power LED will be lit and Atmel Studio will autodetect which Xplained Pro evaluation- and extension kit(s) that's connected. You'll be presented with relevant information like datasheets and kit documentation. You also have the option to launch Atmel Software Framework (ASF) example applications. The target device is programmed and debugged by the on-board Embedded Debugger and no external programmer or debugger tool is needed. Please refer to the Atmel Studio user guide<sup>2</sup> for information regarding how to compile and program the kit.

# 2.3 Design documentation and related links

The following list contains links to the most relevant documents and software for the ATMEGA256RFR2 Xplained Pro.

- Xplained Pro products <sup>3</sup> Atmel Xplained Pro is a series of small-sized and easy-to-use evaluation kits for 8- and 32-bit Atmel microcontrollers. It consists of a series of low cost MCU boards for evaluation and demonstration of features and capabilities of different MCU families.

- 2. ATMEGA256RFR2 Xplained Pro User Guide 4 PDF version of this User Guide.

- 3. ATMEGA256RFR2 Xplained Pro Design Documentation <sup>5</sup> Package containing schematics, BOM, assembly drawings, 3D plots, layer plots etc.

- 4. Atmel Studio <sup>6</sup> Free Atmel IDE for development of C/C++ and assembler code for Atmel microcontrollers.

- 5. IAR Embedded Workbench® <sup>7</sup> for Atmel AVR®. This is a commercial C/C++ compiler that is available for 8-bit AVR. There is a 30 day evaluation version as well as a 4k code size limited kick-start version available from their website.

- 6. Atmel sample store 8 Atmel sample store where you can order samples of devices.

http://www.atmel.com/system/samplesstore

<sup>1</sup> http://www.atmel.com/atmelstudio

http://www.atmel.com/atmelstudio

<sup>&</sup>lt;sup>3</sup> http://www.atmel.com/XplainedPro

<sup>4</sup> http://www.atmel.com/Images/Atmel-42079-ATMEGA256RFR2-Xplained-Pro\_User-Guide.pdf

http://www.atmel.com/Images/Atmel-42079-ATMEGA256RFR2-Xplained-Pro\_User-Guide.zip

<sup>&</sup>lt;sup>6</sup> http://www.atmel.com/atmelstudio

http://www.iar.com/en/Products/IAR-Embedded-Workbench/AVR/

# 3. Xplained Pro

Xplained Pro is an evaluation platform that provides the full Atmel microcontroller experience. The platform consists of a series of Microcontroller (MCU) boards and extension boards that are integrated with Atmel Studio, have Atmel Software Framework (ASF) drivers and demo code, support data streaming and more. Xplained Pro MCU boards support a wide range of Xplained Pro extension boards that are connected through a set of standardized headers and connectors. Each extension board has an identification (ID) chip to uniquely identify which boards are mounted on a Xplained Pro MCU board. This information is used to present relevant user guides, application notes, datasheets and example code through Atmel Studio. Available Xplained Pro MCU and extension boards can be purchased in the Atmel Web Store<sup>1</sup>.

## 3.1 Embedded Debugger

The ATMEGA256RFR2 Xplained Pro contains the Atmel® Embedded Debugger (EDBG) for on-board debugging. The EDBG is a composite USB device of 3 interfaces; a debugger, Virtual COM Port and Data Gateway Interface (DGI).

In conjunction with Atmel Studio, the EDBG debugger interface can program and debug the ATmega256RFR2. On the ATMEGA256RFR2 Xplained Pro, the JTAG interface is connected between the EDBG and the ATmega256RFR2.

The Virtual COM Port is connected to a UART port on the ATmega256RFR2 (see section "Embedded Debugger implementation" on page 14 for pinout), and provides an easy way to communicate with the target application through a simple terminal software. It offers variable baud rate, parity and stop bit settings. Note that the settings on the target device UART must match the settings given in the terminal software.

The DGI consists of several physical data interfaces for communication with the host computer. Please, see section "Embedded Debugger implementation" on page 14 for available interfaces and pinout. Communication over the interfaces are bidirectional. It can be used to send events and values from the ATmega256RFR2, or as a generic printf-style data channel. Traffic over the interfaces can be timestamped on the EDBG for more accurate tracing of events. Note that timestamping imposes an overhead that reduces maximal throughput. The DGI uses a proprietary protocol, and is thus only compatible with Atmel Studio.

The EDBG controls two LEDs on ATMEGA256RFR2 Xplained Pro, a power LED and a status LED. Table 3.1, "EDBG LED control" shows how the LEDs are controlled in different operation modes.

Table 3.1. EDBG LED control

| Operation mode                     | Power LED                                                          | Status LED                                                                |  |

|------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| Normal operation                   | Power LED is lit when power is applied to the board.               | Activity indicator, LED flashes every time something happens on the EDBG. |  |

| Bootloader mode (idle)             | The power LED and the status LED blinks simultaneously.            |                                                                           |  |

| Bootloader mode (firmware upgrade) | The power LED and the stauts LED blinks in an alternating pattern. |                                                                           |  |

For further documentation on the EDBG, see the EDBG User Guide.

## 3.2 Hardware identification system

All Xplained Pro compatible extension boards have an Atmel ATSHA204 crypto authentication chip mounted. This chip contains information that identifies the extension with its name and some extra data. When an Xplained Pro extension board is connected to an Xplained Pro MCU board the information is read and sent to Atmel Studio. The Atmel Kits extension, installed with Atmel Studio, will give relevant information, code examples and links to relevant documents. Table 3.2, "Xplained Pro ID chip content" shows the data fields stored in the ID chip with example content.

Table 3.2. Xplained Pro ID chip content

| Data Field            | Data Type    | Example Content               |

|-----------------------|--------------|-------------------------------|

| Manufacturer          | ASCII string | Atmel'\0'                     |

| Product Name          | ASCII string | Segment LCD1 Xplained Pro'\0' |

| Product Revision      | ASCII string | 02'\0'                        |

| Product Serial Number | ASCII string | 177402020000010'\0'           |

<sup>1</sup> http://store.atmel.com/

| Data Field           | Data Type | Example Content |

|----------------------|-----------|-----------------|

| Minimum Voltage [mV] | uint16_t  | 3000            |

| Maximum Voltage [mV] | uint16_t  | 3600            |

| Maximum Current [mA] | uint16_t  | 30              |

## 3.3 Power supply

The ATMEGA256RFR2 Xplained Pro kit can be powered either by USB or by an external power source through the 4-pin power header, marked PWR. This connector is described in "Power header" on page 8. The available power sources and specifications are listed in Table 3.3, "Power sources for ATMEGA256RFR2 Xplained Pro".

Table 3.3. Power sources for ATMEGA256RFR2 Xplained Pro

| Power input              | Voltage requirements                  | Current requirements                                                                                   | Connector marking |

|--------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|

| External power           | 4.3 V to 5.5 V                        | Recommended minimum is 500mA to be able to provide enough current for extentions and the board itself. | PWR               |

|                          |                                       | Recommended maximum is 2A due to the input protection maximum current specification.                   |                   |

| Embedded debugger<br>USB | 4.4V to 5.25V (according to USB spec) | 500 mA (according to USB spec)                                                                         | DEBUG USB         |

The kit will automatically detect which power sources are available and choose which one to use according to the following priority:

- 1. External power

- 2. Embedded debugger USB

## 3.3.1 Measuring ATmega256RFR2 power consumption

As part of an evaluation of the ATmega256RFR2 it can be of interest to measure its power consumption. Because the device has a separate power plane (VCC\_MCU\_P3V3) on this board it is possible to measure the current consumption by measuring the current that is flowing into this plane. The VCC\_MCU\_P3V3 plane is connected via a jumper to the main power plane (VCC\_TARGET\_P3V3) and by replacing the jumper with an ampere meter it is possible to determine the current consumption. To locate the current measurement header, please refer to Figure 1.1, "ATMEGA256RFR2 Xplained Pro evaluation kit overview."

#### Warning

Do not power the board without having the jumper or an ampere meter mounted. This can cause the ATmega256RFR2 to be powered through its I/O pins and cause undefined operation of the device.

#### 3.4 Standard headers and connectors

#### 3.4.1 Xplained Pro standard extension header

All Xplained Pro kits contains one or more dual row, 20 pin, 100mil extension headers. Xplained Pro MCU boards have male headers while Xplained Pro extensions have their female counterparts. Note that all pins are not always connected; However, all the connected pins follow the defined pin-out described in Table 3.4, "Standard extension header". The extension headers can be used to connect a wide variety of Xplained Pro extensions to Xplained Pro MCU boards and to access the pins of the target MCU on Xplained Pro MCU board directly.

Table 3.4. Standard extension header

| Pin number | Name | Description                                           |

|------------|------|-------------------------------------------------------|

| 1          | ID   | Communication line to the ID chip on extension board. |

| Pin number | Name          | Description                                                                                |

|------------|---------------|--------------------------------------------------------------------------------------------|

| 2          | GND           | Ground                                                                                     |

| 3          | ADC(+)        | Analog to digital converter , alternatively positive part of differential ADC              |

| 4          | ADC(-)        | Analog to digital converter , alternatively negative part of differential ADC              |

| 5          | GPIO1         | General purpose IO                                                                         |

| 6          | GPIO2         | General purpose IO                                                                         |

| 7          | PWM(+)        | Pulse width modulation , alternatively positive part of differential PWM                   |

| 8          | PWM(-)        | Pulse width modulation , alternatively positive part of differential PWM                   |

| 9          | IRQ/GPIO      | Interrupt request line and/or general purpose IO.                                          |

| 10         | SPI_SS_B/GPIO | Slave select for SPI and/or general purpose IO.                                            |

| 11         | TWI_SDA       | Data line for two wire interface. Always implemented, bus type.                            |

| 12         | TWI_SCL       | Clock line for two wire interface. Always implemented, bus type.                           |

| 13         | USART_RX      | Receiver line of Universal Synchronous and Asynchronous serial Receiver and Transmitter    |

| 14         | USART_TX      | Transmitter line of Universal Synchronous and Asynchronous serial Receiver and Transmitter |

| 15         | SPI_SS_A      | Slave select for SPI. Should be unique if possible.                                        |

| 16         | SPI_MOSI      | Master out slave in line of Serial peripheral interface. Always implemented, bus type      |

| 17         | SPI_MISO      | Master in slave out line of Serial peripheral interface. Always implemented, bus type      |

| 18         | SPI_SCK       | Clock for Serial peripheral interface. Always implemented, bus type                        |

| 19         | GND           | Ground                                                                                     |

| 20         | VCC           | Power for extension board                                                                  |

#### 3.4.2 Power header

The power header can be used to connect external power to the ATMEGA256RFR2 Xplained Pro kit. The kit will automatically detect and switch to the external power if supplied. The power header can also be used as supply for external peripherals or extension boards. Care must be taken not to exceed the total current limitation of the on-board regulator for the 3.3V regulated output. To locate the current measurement header, please refer to Figure 1.1, "ATMEGA256RFR2 Xplained Pro evaluation kit overview."

Table 3.5. Power header PWR

| Pin number PWR header | Pin name  | Description                                                    |

|-----------------------|-----------|----------------------------------------------------------------|

| 1                     | VEXT_P5V0 | External 5V input                                              |

| 2                     | GND       | Ground                                                         |

| 3                     | VCC_P5V0  | Unregulated 5V (output, derived from one of the input sources) |

| 4                     | VCC_P3V3  | Regulated 3.3V (output, used as main power for the kit)        |

Note

If the board is powered from a battery source it is recommended to use the PWR header. If there is a power source connected to EDBG USB, the EDBG is activated and it will consume more power.

# 4. Hardware user guide

## 4.1 Connectors

This chapter describes the implementation of the relevant connectors and headers on ATMEGA256RFR2 Xplained Pro and their connection to the ATmega256RFR2. The tables of connections in this chapter also describes which signals are shared between the headers and on-board functionality.

#### 4.1.1 I/O extension headers

The ATMEGA256RFR2 Xplained Pro headers EXT1, EXT2, EXT3, EXT4 and EXT5 offers access to the I/O of the microcontroller in order to expand the board e.g. by connecting extension modules to the board. These headers all comply with the standard extension header specified in Xplained Pro Standard Extension Header. All headers have a pitch of 2.54 mm.

Table 4.1. Extension header EXT1

| Pin on EXT1 | ATmega256RFR2 pin | Function                                          | Shared functionality                                             |

|-------------|-------------------|---------------------------------------------------|------------------------------------------------------------------|

| 1           |                   | Communication line to ID chip on extension board. |                                                                  |

| 2           |                   | GND                                               |                                                                  |

| 3           | PF0               | ADC0                                              |                                                                  |

| 4           | PF1               | ADC1                                              |                                                                  |

| 5           | PE2               | GPIO                                              |                                                                  |

| 6           | PE3               | GPIO                                              |                                                                  |

| 7           | PB5               | OC1A                                              | EXT4 header.                                                     |

| 8           | PB6               | OC1B                                              |                                                                  |

| 9           | PE5               | GPIO / INT5                                       | EXT4 header.                                                     |

| 10          | PD5               | GPIO / SPI chip select B                          | EXT4 header.                                                     |

| 11          | PD1               | TWI SDA                                           | All EXT headers.                                                 |

| 12          | PD0               | TWI SCL                                           | All EXT headers.                                                 |

| 13          | PE0               | UARTO RXD                                         | All EXT headers. EXT2, EXT3 and EXT5 connected through cutstrap. |

| 14          | PE1               | UART0 TXD                                         | All EXT headers. EXT2, EXT3 and EXT5 connected through cutstrap. |

| 15          | PG0               | GPIO / SPI chip select A                          | EXT4 header.                                                     |

| 16          | PB2               | SPI MOSI                                          | All EXT headers.                                                 |

| 17          | PB3               | SPI MISO                                          | All EXT headers.                                                 |

| 18          | PB1               | SPI SCK                                           | All EXT headers.                                                 |

| 19          |                   | GND                                               |                                                                  |

| 20          |                   | VCC                                               |                                                                  |

Table 4.2. Extension header EXT2

| Pin on EXT2 | ATmega256RFR2 pin | Function                                          | Shared functionality |

|-------------|-------------------|---------------------------------------------------|----------------------|

| 1           |                   | Communication line to ID chip on extension board. |                      |

| 2           |                   | GND                                               |                      |

| Pin on EXT2 | ATmega256RFR2 pin | Function                 | Shared functionality                                                              |

|-------------|-------------------|--------------------------|-----------------------------------------------------------------------------------|

| 3           |                   |                          |                                                                                   |

| 4           |                   |                          |                                                                                   |

| 5           |                   |                          |                                                                                   |

| 6           |                   |                          |                                                                                   |

| 7           |                   |                          |                                                                                   |

| 8           |                   |                          |                                                                                   |

| 9           | PE6               | GPIO / INT6              | EXT5 header.                                                                      |

| 10          | PD6               | GPIO / SPI chip select B | EXT5 header.                                                                      |

| 11          | PD1               | TWI SDA                  | All other EXT headers.                                                            |

| 12          | PD0               | TWI SCL                  | All other EXT headers.                                                            |

| 13          | PE0 <sup>1</sup>  | UARTO RXD                | All other EXT headers.<br>EXT2, EXT3 and EXT5<br>connected through cut-<br>strap. |

| 14          | PE1 <sup>1</sup>  | UART0 TXD                | All other EXT headers.<br>EXT2, EXT3 and EXT5<br>connected through cut-<br>strap. |

| 15          | PD4               | GPIO / SPI chip select A | EXT5 header.                                                                      |

| 16          | PB2               | SPI MOSI                 | All other EXT headers.                                                            |

| 17          | PB3               | SPI MISO                 | All other EXT headers.                                                            |

| 18          | PB1               | SPI SCK                  | All other EXT headers.                                                            |

| 19          |                   | GND                      |                                                                                   |

| 20          |                   | VCC                      |                                                                                   |

Notes: <sup>1</sup>Connected through cut-strap

Table 4.3. Extension header EXT3

| Pin on EXT3 | ATmega256RFR2 pin | Function                                          | Shared functionality                                                              |

|-------------|-------------------|---------------------------------------------------|-----------------------------------------------------------------------------------|

| 1           |                   | Communication line to ID chip on extension board. |                                                                                   |

| 2           |                   | GND                                               |                                                                                   |

| 3           | PF3               | GPIO                                              |                                                                                   |

| 4           | PG5               | GPIO                                              |                                                                                   |

| 5           | PB7               | GPIO                                              |                                                                                   |

| 6           |                   |                                                   |                                                                                   |

| 7           |                   |                                                   |                                                                                   |

| 8           |                   |                                                   |                                                                                   |

| 9           | PE7               | GPIO / INT7                                       |                                                                                   |

| 10          | PD7               | GPIO / SPI chip select B                          |                                                                                   |

| 11          | PD1               | TWI SDA                                           | All other EXT headers.                                                            |

| 12          | PD0               | TWI SCL                                           | All other EXT headers.                                                            |

| 13          | PE0 <sup>1</sup>  | UARTO RXD                                         | All other EXT headers.<br>EXT2, EXT3 and EXT5<br>connected through cut-<br>strap. |

| 14          | PE1 <sup>1</sup>  | UART0 TXD                                         | All other EXT headers. EXT2, EXT3 and EXT5                                        |

| Pin on EXT3 | ATmega256RFR2 pin | Function                 | Shared functionality             |

|-------------|-------------------|--------------------------|----------------------------------|

|             |                   |                          | connected through cut-<br>strap. |

| 15          | PG4               | GPIO / SPI chip select A |                                  |

| 16          | PB2               | SPI MOSI                 | All other EXT headers.           |

| 17          | PB3               | SPI MISO                 | All other EXT headers.           |

| 18          | PB1               | SPI SCK                  | All other EXT headers.           |

| 19          |                   | GND                      |                                  |

| 20          |                   | VCC                      |                                  |

<sup>1</sup>Connected through cut-strap Notes:

Table 4.4. Extension header EXT4

| Pin on EXT4 | ATmega256RFR2 pin | Function                                          | Shared functionality                                                              |

|-------------|-------------------|---------------------------------------------------|-----------------------------------------------------------------------------------|

| 1           |                   | Communication line to ID chip on extension board. |                                                                                   |

| 2           |                   | GND                                               |                                                                                   |

| 3           |                   |                                                   |                                                                                   |

| 4           |                   |                                                   |                                                                                   |

| 5           |                   |                                                   |                                                                                   |

| 6           |                   |                                                   |                                                                                   |

| 7           | PB5               | OC1A                                              | EXT1 header.                                                                      |

| 8           |                   |                                                   |                                                                                   |

| 9           | PE5               | GPIO / INT5                                       | EXT1 header.                                                                      |

| 10          | PG0               | GPIO / SPI chip select B                          | EXT1 header.                                                                      |

| 11          | PD1               | TWI SDA                                           | All other EXT headers.                                                            |

| 12          | PD0               | TWI SCL                                           | All other EXT headers.                                                            |

| 13          | PE0               | UARTO RXD                                         | All other EXT headers.<br>EXT2, EXT3 and EXT5<br>connected through cut-<br>strap. |

| 14          | PE1               | UARTO TXD                                         | All other EXT headers.<br>EXT2, EXT3 and EXT5<br>connected through cut-<br>strap. |

| 15          | PD5               | GPIO / SPI chip select A                          | EXT1 header.                                                                      |

| 16          | PB2               | SPI MOSI                                          | All other EXT headers.                                                            |

| 17          | PB3               | SPI MISO                                          | All other EXT headers.                                                            |

| 18          | PB1               | SPI SCK                                           | All other EXT headers.                                                            |

| 19          |                   | GND                                               |                                                                                   |

| 20          |                   | VCC                                               |                                                                                   |

Table 4.5. Extension header EXT5

| Pin on EXT5 | ATmega256RFR2 pin | Function                                          | Shared functionality |

|-------------|-------------------|---------------------------------------------------|----------------------|

| 1           |                   | Communication line to ID chip on extension board. |                      |

| 2           |                   | GND                                               |                      |

| 3           |                   |                                                   |                      |

| Pin on EXT5 | ATmega256RFR2 pin | Function                 | Shared functionality                                                              |

|-------------|-------------------|--------------------------|-----------------------------------------------------------------------------------|

| 4           |                   |                          |                                                                                   |

| 5           |                   |                          |                                                                                   |

| 6           |                   |                          |                                                                                   |

| 7           |                   |                          |                                                                                   |

| 8           |                   |                          |                                                                                   |

| 9           | PE6               | GPIO / INT6              | EXT2 header.                                                                      |

| 10          | PD4               | GPIO / SPI chip select B | EXT2 header.                                                                      |

| 11          | PD1               | TWI SDA                  | All other EXT headers.                                                            |

| 12          | PD0               | TWI SCL                  | All other EXT headers.                                                            |

| 13          | PE0 <sup>1</sup>  | UARTO RXD                | All other EXT headers.<br>EXT2, EXT3 and EXT5<br>connected through cut-<br>strap. |

| 14          | PE1 <sup>1</sup>  | UART0 TXD                | All other EXT headers.<br>EXT2, EXT3 and EXT5<br>connected through cut-<br>strap. |

| 15          | PD6               | GPIO / SPI chip select A | EXT2 header.                                                                      |

| 16          | PB2               | SPI MOSI                 | All other EXT headers.                                                            |

| 17          | PB3               | SPI MISO                 | All other EXT headers.                                                            |

| 18          | PB1               | SPI SCK                  | All other EXT headers.                                                            |

| 19          |                   | GND                      |                                                                                   |

| 20          |                   | VCC                      |                                                                                   |

Notes: <sup>1</sup>Co

<sup>1</sup>Connected through cut-strap

#### 4.1.2 Other headers

In addition to the "I/O extension headers" on page 9, ATMEGA256RFR2 Xplained Pro has additionally two headers with spare signals which offers access to the I/O of the microcontroller which are otherwise not easily available elsewhere or might be favourable to have collected toghether. All headers have a pitch of 2.54mm.

Table 4.6. SPARE ADC signals header

| Pin on header | ATmega256RFR2<br>pin | Function          | Shared functionality |

|---------------|----------------------|-------------------|----------------------|

| 1             | -                    | VCC (3.3V)        |                      |

| 2             | PF4                  | ADC4 <sup>1</sup> | JTAG Interface, TCK  |

| 3             | PF5                  | ADC5 <sup>1</sup> | JTAG Interface, TMS  |

| 4             | PF6                  | ADC6 <sup>1</sup> | JTAG Interface, TDO  |

| 5             | PF7                  | ADC7 <sup>1</sup> | JTAG Interface, TDI  |

Notes:

<sup>1</sup>These lines are connected to the JTAG interface, and ADC will not work properly while debugging or programming the kit.

Table 4.7. SPARE signals header 2

| Pin on header | ATmega256RFR2<br>pin | Function                     | Shared functionality  |

|---------------|----------------------|------------------------------|-----------------------|

| 1             | AREF                 | Analog reference             |                       |

| 2             | TST                  | Test pin for RF test mode    |                       |

| 3             | RSTN                 | Reset                        | EDBG and RESET button |

| 4             | RSTON                | Reset status                 |                       |

| 5             | CLKI                 | Alternative main clock input |                       |

| Pin on header | ATmega256RFR2<br>pin | Function | Shared functionality |

|---------------|----------------------|----------|----------------------|

| 6             |                      | GND      |                      |

## 4.2 Peripherals

#### 4.2.1 Crystals

The ATMEGA256RFR2 Xplained Pro kit contains two crystals that can be used as clock sources for the ATmega256RFR2 device. Each crystal has a cut-strap next to it that can be used to measure the oscillator allowance. This is done by cutting the strap and adding a resistor across the strap. More information about oscillator allowance and safety factor can be found in appnote AVR4100<sup>1</sup>

Table 4.8. External 32.768kHz crystals

| Pin on ATmega256RFR2 | Function              |

|----------------------|-----------------------|

| PG3                  | TOSC2, crystal output |

| PG4                  | TOSC1, crystal input  |

#### Table 4.9. External 12MHz crystals

| Pin on ATmega256RFR2 | Function       |

|----------------------|----------------|

| XTAL1                | Crystal input  |

| XTAL2                | Crystal output |

#### 4.2.2 Mechanical buttons

ATMEGA256RFR2 Xplained Pro contains two mechanical buttons. One button is the RESET button connected to the ATmega256RFR2 reset line and the other is a generic user configurable button. When a button is pressed it will drive the I/O line to GND.

Table 4.10. Mechanical buttons

| Pin on ATmega256RFR2 | Silkscreen text |

|----------------------|-----------------|

| RSTN                 | RESET           |

| PE4                  | SW0             |

#### 4.2.3 LED

There is one yellow LED available on the ATMEGA256RFR2 Xplained Pro board that can be turned on and off. The LED can be activated by driving the connected I/O line to GND.

Table 4.11. LED connections

| Pin on ATmega256RFR2 | LED        |

|----------------------|------------|

| PB4                  | Yellow LED |

#### 4.2.4 RF

The main feature of ATMEGA256RFR2 Xplained Pro is to show the RF capability of the ATmega256RFR2 device. This device has bidirectional differential antenna pins, which are fed through a balun (Johanson Technology, 2450BM15A0015<sup>2</sup>) to create a single unbalanced output/input. This kit has a passive analog RF switch (Skyworks Solutions Inc, AS222-92LF<sup>3</sup>) connected to the unbalanced output of the balun. The switch is driven by the DIG1 and DIG2 pins of the ATmega256RFR2 which feature Antenna Diversity to enable the device to automatically select the best signal from two antennas (can also be selected manually). The output of the switch is connected to a ceramic chip antenna (Johanson Technology, 2540AT18D0100<sup>4</sup>) and a SMA connector for external antennas.

<sup>&</sup>lt;sup>4</sup> http://www.johansontechnology.com/images/stories/ip/rf-antennas/Antenna\_2450AT18D0100\_v3.pdf

<sup>1</sup> http://www.atmel.com/images/doc8333.pdf

<sup>&</sup>lt;sup>2</sup> http://www.johansontechnology.com/datasheets/balun-filter/2450BM15A0015.pdf

http://www.skyworksinc.com/uploads/documents/200252C.pdf

#### Table 4.12. RF connections

| Pin on ATmega256RFR2 |                               |

|----------------------|-------------------------------|

| RFP                  | RF balanced output (Positive) |

| RFN                  | RF balanced output (Negative) |

#### 4.2.5 Temperature sensor

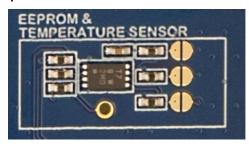

ATMEGA256RFR2 Xplained Pro features an Atmel AT30TSE758 temperature sensor chip with an 8kbit serial EEPROM inside. The sensor includes programmable high and low temperature alarms, user-selectable temperature resolution up to 12 bits, and an I2C/SMBus™ compatible serial interface.

Table 4.13. Temperature sensor connections.

| AT30TSE758<br>temperature<br>sensor pin | Pin name | Pin on<br>ATmega256RFR | Comment                                                  |

|-----------------------------------------|----------|------------------------|----------------------------------------------------------|

| 1                                       | SDA      | PD1                    | Data line of serial interface                            |

| 2                                       | SCL      | PD0                    | Clock line of serial interface                           |

| 3                                       | ALERT    | NC <sup>1</sup>        | Temperature alarm signalling pin                         |

| 4                                       | GND      | GND                    |                                                          |

| 5                                       | A2       | -                      | Addres line for serial interface, by default pulled low  |

| 6                                       | A1       | -                      | Addres line for serial interface, by default pulled high |

| 7                                       | A0       | -                      | Addres line for serial interface, by default pulled high |

| 8                                       | VCC      | VCC                    |                                                          |

Notes: <sup>1</sup>Alert pin is available on a testpoint hole close to the sensor.

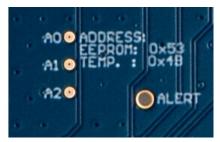

The temperature sensor has two TWI addresses, one for the temperature sensor and one for the EEPROM. The addresses are "0b1001 A2 A1 A0" for the temperature sensor and "0b1010 A2 A1 A0" for the EEPROM. The address selection lines (A2, A1 and A0) of the temperature sensor chip is by default pulled high for A0 and A1 and low for A2, through  $100k\Omega$  resistors, which makes the default addresses 0b1001011 and 0b1010011. Soldering the the straps on the front of the ATMEGA256RFR2 Xplained Pro board for An will alter that bit in the address to low or high. Each strap is marked in silkscreen with A0, A1 and A2 as shown in Figure 4.1, "Temperature sensor TWI address." When communicating with the EEPROM, part of the TWI address is used as a page address, for more details see the device datasheet.

Figure 4.1. Temperature sensor TWI address.

### 4.3 Embedded Debugger implementation

The ATMEGA256RFR2 Xplained Pro contains an Embedded Debugger (EDBG) that can be used to program and debug the ATmega256RFR2 using JTAG. The Embedded Debugger also include a Virtual Comport interface over UART, an Atmel Data Gateway Interface over SPI and TWI and it monitors four of the ATmega256RFR2 GPIOs. Atmel Studio can be used as a front end for the Embedded Debugger.

#### 4.3.1 JTAG

The JTAG use five pins to communicate with the target. For further information on how to use the programming and debugging capabilities of the EDBG, see "Embedded Debugger" on page 6.

<sup>&</sup>lt;sup>5</sup> http://www.atmel.com/Images/doc8751.pdf

Table 4.14. JTAG connections.

| Pin on ATmega256RFR2 | Function |

|----------------------|----------|

| PF4                  | JTAG TCK |

| PF5                  | JTAG TMS |

| PF6                  | JTAG TDO |

| PF7                  | JTAG TDI |

| RSTN                 | RESET    |

### 4.3.2 Virtual COM port

The Embedded Debugger act as a Virtual Com Port gateway by using one of the ATmega256RFR2 UARTs. For further information on how to use the Virtual COM port see "Embedded Debugger" on page 6.

Table 4.15. Virtual COM port connections.

| Pin on ATmega256RFR2 | Function                         |

|----------------------|----------------------------------|

| PD2                  | UART RXD (ATmega256RFR2 RX line) |

| PD3                  | UART TXD (ATmega256RFR2 TX line) |

#### 4.3.3 Atmel Data Gateway Interface

The Embedded Debugger features an Atmel Data Gateway Interface (DGI) by using either a SPI or TWI port. The DGI can be used to send a variety of data from the ATmega256RFR2 to the host PC. For further information on how to use the DGI interface see "Embedded Debugger" on page 6.

Table 4.16. DGI interface connections when using SPI.

| Pin on ATmega256RFR2 | Function                               |

|----------------------|----------------------------------------|

| PB0                  | Slave select (ATmega256RFR2 is Master) |

| PB1                  | SPI SCK (Clock Out)                    |

| PB2                  | SPI MOSI (Master Out, Slave in)        |

| PB3                  | SPI MISO (Master In, Slave Out)        |

Table 4.17. DGI interface connections when using TWI.

| Pin on ATmega256RFR2 | Function         |

|----------------------|------------------|

| PD0                  | SCL (Clock line) |

| PD1                  | SDA (Data line)  |

Four GPIO lines are connected to the Embedded Debugger. The EDBG can monitor these lines and time stamp pin value changes. This makes it possible to accurately time stamp events in the ATmega256RFR2 application code. For further information on how to configure and use the GPIO monitoring features see "Embedded Debugger" on page 6.

Table 4.18. GPIO lines connected to the EDBG.

| Pin on ATmega256RFR2 | Function |

|----------------------|----------|

| PE2                  | GPIO0    |

| PE3                  | GPIO1    |

| PE5                  | GPIO2    |

| PE6                  | GPIO3    |

# 5. Hardware revision history and known issues

## 5.1 Identifying product ID and revision

The revision and product identifier of Xplained Pro boards can be found in two ways, through Atmel Studio or by looking at the sticker on the bottom side of the PCB.

By connecting a Xplained Pro MCU board to a computer with Atmel Studio running, an information window will pop up. The first 6 digits of the serial number, which is listed under kit details, contain the product identifier and revision. Information about connected Xplained Pro extension boards will also appear in the Atmel Kits window.

The same information can be found on the sticker on the bottom side of the PCB. Most kits will print the identifier and revision in plain text as *A09-nnnn\rr* where *nnnn* is the identifier and *rr* is the revision. Boards with limited space have a sticker with only a QR-code which contains a serial number string.

The serial number string has the following format:

```

"nnnnrrsssssssss"

n = product identifier

r = revision

s = serial number

```

The kit identifier for ATMEGA256RFR2 Xplained Pro is 1784.

## 5.2 Revision 3

Revision 3 of ATMEGA256RFR2 Xplained Pro is the initial released version.

#### **Document revision history** 6.

| Doc. Rev. | Date       | Comment       |

|-----------|------------|---------------|

| Α         | 25.02.2013 | First release |

# 7. Evaluation board/kit important notice

## 7.1 Evaluation board/kit important notice

This evaluation board/kit is intended for use for **FURTHER ENGINEERING**, **DEVELOPMENT**, **DEMONSTRATION**, **OR EVALUATION PURPOSES ONLY**. It is not a finished product and may not (yet) comply with some or any technical or legal requirements that are applicable to finished products, including, without limitation, directives regarding electromagnetic compatibility, recycling (WEEE), FCC, CE or UL (except as may be otherwise noted on the board/kit). Atmel supplied this board/kit "AS IS," without any warranties, with all faults, at the buyer's and further users' sole risk. The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies Atmel from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge and any other technical or legal concerns.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER USER NOR ATMEL SHALL BE LIABLE TO EACH OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

No license is granted under any patent right or other intellectual property right of Atmel covering or relating to any machine, process, or combination in which such Atmel products or services might be or are used.

Mailing Address: Atmel Corporation, 1600 Technology Drive, San Jose, CA 95110

Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200 | www.atmel.com

$\ensuremath{\texttt{©}}$  2013 Atmel Corporation. All rights reserved. / Rev.: 42079A-MCU-02/13

Atmel®, Atmel logo and combinations thereof, AVR®, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Windows® is a registered trademark of Microsoft Corporation in U.S. and or other countries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.